# TQMxE41S Preliminary User's Manual

TQMxE41S UM 0100 11.12.2023

# TABLE OF CONTENTS

| 1.      | ABOUT THIS MANUAL                                 |          |

|---------|---------------------------------------------------|----------|

| 1.1     | Copyright and Licence Expenses                    | 1        |

| 1.2     | Registered Trademarks                             | 1        |

| 1.3     | Disclaimer                                        | 1        |

| 1.4     | Imprint                                           | 1        |

| 1.5     | Service and Support                               | 1        |

| 1.6     | Tips on Safety                                    |          |

| 1.7     | Symbols and Typographic Conventions               | 2        |

| 1.8     | Handling and ESD Tips                             | 2        |

| 1.9     | Naming of Signals                                 |          |

| 1.10    | Further Applicable Documents / Presumed Knowledge | 3        |

| 2.      | INTRODUCTION                                      | ∠        |

| 2.1     | Functional Overview                               | ∠        |

| 2.2     | SMARC Specification Compliance                    | 5        |

| 2.3     | TQMxE41S Variants                                 | 5        |

| 2.4     | Accessories                                       | 5        |

| 3.      | FUNCTION                                          | <i>6</i> |

| 3.1     | TQMxE41S Block Diagram                            | <i>6</i> |

| 3.2     | Electrical Characteristics                        | e        |

| 3.2.1   | Supply Voltage                                    | e        |

| 3.2.2   | Power Consumption                                 |          |

| 3.2.2.1 | Real Time Clock Power Consumption                 |          |

| 3.3     | Environmental conditions                          |          |

| 3.4     | System Components                                 |          |

| 3.4.1   | CPUs                                              |          |

| 3.4.2   | Graphics                                          |          |

| 3.4.3   | Memory                                            |          |

| 3.4.3.1 | LPDDR5 SDRAM                                      |          |

| 3.4.3.2 | eMMC                                              |          |

| 3.4.3.3 | SPI Boot Flash                                    |          |

| 3.4.3.4 | EEPROM                                            |          |

| 3.4.4   | Real Time Clock                                   |          |

| 3.4.5   | Trusted Platform Module                           |          |

| 3.4.6   | TQ flexible I/O configuration (TQ-flexiCFG)       |          |

| 3.5     | Interfaces                                        |          |

| 3.5.1   | PCI Express                                       |          |

| 3.5.2   | Serial ATA                                        |          |

| 3.5.3   | Gigabit Ethernet                                  |          |

| 3.5.4   | Digital Display Interface                         |          |

| 3.5.5   | LVDS Interface                                    |          |

| 3.5.6   | USB 2.0 Interfaces                                |          |

| 3.5.7   | USB 3.0 Interfaces                                |          |

| 3.5.8   | General Purpose Input/Output                      |          |

| 3.5.9   | Audio Interfaces                                  |          |

| 3.5.10  | I <sup>2</sup> C Bus                              |          |

| 3.5.10  | SMBus / Power Management I <sup>2</sup> C Bus     |          |

|         | Serial Peripheral Interface                       |          |

| 3.5.12  | ·                                                 |          |

| 3.5.13  | eSPI                                              |          |

| 3.5.14  | Serial Ports                                      |          |

| 3.5.15  | Watchdog Timer                                    |          |

| 3.6     | Connectors & LEDs                                 |          |

| 3.6.1   | SMARC Connector                                   |          |

| 3.6.2   | Debug LED                                         |          |

| 3.7     | SMARC Connector Pinout                            |          |

| 3.7.1   | Signal Assignment Abbreviations                   |          |

| 3.7.2   | SMARC Connector Pin Assignment                    |          |

| 4.      | MECHANICS                                         |          |

| 4.1     | TQMxE41S Dimensions                               |          |

| 4.2     | Heat Spreader Dimensions                          | 21       |

| 4.3                  | Mechanical and Thermal Considerations                        | 21 |

|----------------------|--------------------------------------------------------------|----|

| 4.4                  | Protection against external effects                          | 21 |

| 5.                   | SOFTWARE                                                     | 22 |

| 5.1                  | System Resources                                             | 22 |

| 5.1.1                | l <sup>2</sup> C Bus                                         | 22 |

| 5.1.2                | SMBus                                                        | 22 |

| 5.1.3                | Memory Map                                                   | 22 |

| 5.1.4                | IRQ Map                                                      | 22 |

| 5.2                  | Operating Systems                                            |    |

| 5.2.1                | Supported Operating Systems                                  |    |

| 5.2.2                | Driver Download                                              |    |

| 5.3                  | TQ-Systems Embedded Application Programming Interface (EAPI) |    |

| 5.4                  | Software Tools                                               |    |

| 5. <del></del><br>6. | BIOS – MENU                                                  |    |

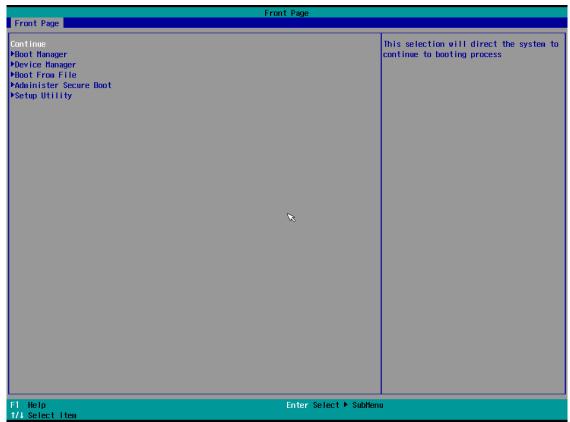

| 6.1                  | Continue                                                     |    |

| 6.2                  |                                                              |    |

|                      | Boot Manager                                                 |    |

| 6.3                  | Device Manager                                               |    |

| 6.3.1                | Driver Health Manager                                        |    |

| 6.3.2                | Network Device List                                          |    |

| 6.4                  | Boot from File                                               |    |

| 6.5                  | Administer Secure Boot                                       |    |

| 6.6                  | Setup Utility                                                |    |

| 6.6.1                | Main                                                         |    |

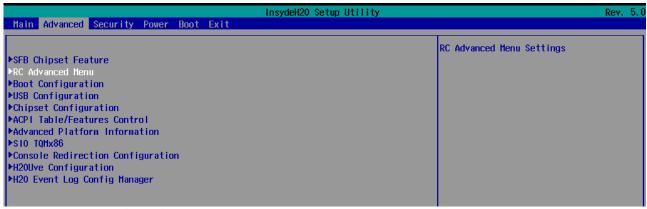

| 6.6.2                | Advanced                                                     | 27 |

| 6.6.2.1              | SFB Chipset Feature                                          | 27 |

| 6.6.2.2              | RC Advanced Menu                                             | 28 |

| 6.6.2.3              | Boot Configuration                                           | 48 |

| 6.6.2.4              | USB Configuration                                            | 48 |

| 6.6.2.5              | Chipset Configuration                                        |    |

| 6.6.2.6              | ACPI Table/Features Control                                  |    |

| 6.6.2.7              | SIO TQMx86                                                   |    |

| 6.6.2.8              | Console Redirection Configuration                            |    |

| 6.6.2.9              | H20Uve Configuration                                         |    |

| 6.6.2.10             | H20 Event Log Config Manager                                 |    |

| 6.6.3                | Security                                                     |    |

| 6.6.4                | Power                                                        |    |

| 6.6.5                | Boot                                                         |    |

| 6.6.6                | Exit                                                         |    |

|                      |                                                              |    |

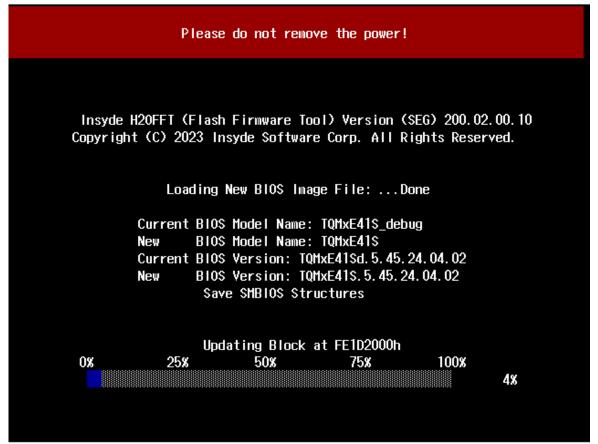

| 7.                   | BIOS – UPDATE                                                |    |

| 7.1.1                | Step 1: Preparing USB Stick                                  |    |

| 7.1.2                | Step 2: Preparing Management Engine (ME) FW for update       |    |

| 7.1.3                | Step 3a: Updating uEFI BIOS via EFI Shell                    |    |

| 7.1.4                | Step 3b: Updating uEFI BIOS via Windows Operating System     |    |

| 7.1.5                | Step 4: BIOS update check on the TQMxE41S Module             |    |

| 8.                   | SAFETY REQUIREMENTS AND PROTECTIVE REGULATIONS               | 58 |

| 8.1                  | EMC                                                          | 58 |

| 8.2                  | ESD                                                          | 58 |

| 8.3                  | Shock & Vibration                                            | 58 |

| 8.4                  | Operational Safety and Personal Security                     | 58 |

| 8.5                  | Intended Use                                                 |    |

| 8.6                  | Export Control and Sanctions Compliance                      | 59 |

| 8.7                  | Warranty                                                     |    |

| 8.8                  | Statement on California Proposition 65                       |    |

| 8.9                  | Reliability and Service Life                                 |    |

| 9.                   | ENVIRONMENT PROTECTION                                       |    |

| 9.<br>9.1            | RoHS                                                         |    |

| 9.1                  | WEEE <sup>®</sup>                                            |    |

|                      |                                                              |    |

| 9.3                  | REACH®                                                       |    |

| 9.4                  | EuP                                                          |    |

| 9.5                  | Battery                                                      |    |

| 9.6                  | Packaging                                                    |    |

| 9.7                  | Other Entries                                                |    |

| 10.                  | APPENDIX                                                     |    |

| 10.1                 | Acronyms and Definitions                                     | 61 |

| 10.2                 | References                                                   | 63 |

# **TABLE DIRECTORY**

| Table 1:  | Terms and Conventions                                        | 2  |

|-----------|--------------------------------------------------------------|----|

| Table 2:  | TQMxE41S Power Consumption                                   | 7  |

| Table 3:  | RTC Current Consumption                                      | 8  |

| Table 4:  | Intel® X7000E Series: Comparison of the SKUs                 |    |

| Table 5:  | Maximum Resolution                                           | 10 |

| Table 6:  | PCI Express Configuration Options                            | 11 |

| Table 7:  | LED Boot Messages                                            |    |

| Table 8:  | Abbreviations used                                           | 14 |

| Table 9:  | SMARC Connector Pin Assignment                               | 15 |

| Table 10: | I <sup>2</sup> C Address Mapping on GP I <sup>2</sup> C Port | 22 |

| Table 11: | Acronyms                                                     | 61 |

| Table 12: | Further Applicable Documents and Links                       | 63 |

# FIGURE DIRECTORY

| Figure 1:  | Block Diagram TQMxE41S             | 6  |

|------------|------------------------------------|----|

| Figure 2:  | InsydeH2O BIOS Front Page          |    |

| Figure 3:  | RC Advanced menu                   |    |

| Figure 4:  | PCH-FW Configuration menu          |    |

| Figure 5:  | Firmware Update Configuration menu |    |

| Figure 6:  | ME FW Image Re-Flash option        |    |

| Figure 7:  | EFI Shell                          |    |

| Figure 8:  | EFI Shell uEFI BIOS Update         |    |

| Figure 9:  | Screen during BIOS Update          |    |

| Figure 10: | FFI BIOS Main Menu                 | 57 |

# **REVISION HISTORY**

| Rev. | Date       | Name | Pos. | Modification    |

|------|------------|------|------|-----------------|

| 0100 | 11.12.2023 | PD   |      | Initial release |

#### 1. ABOUT THIS MANUAL

#### 1.1 Copyright and Licence Expenses

Copyright protected © 2023 by TQ-Systems GmbH.

This Preliminary User's Manual may not be copied, reproduced, translated, changed or distributed, completely or partially in electronic, machine readable, or in any other form without the written consent of TQ-Systems GmbH.

The drivers and utilities for the components used as well as the BIOS are subject to the copyrights of the respective manufacturers. The licence conditions of the respective manufacturer are to be adhered to.

BIOS-licence expenses are paid by TQ-Systems GmbH and are included in the price.

Licence expenses for the Operating System and applications are not taken into consideration and must be calculated / declared separately.

#### 1.2 Registered Trademarks

TQ-Systems GmbH aims to adhere to copyrights of all graphics and texts used in all publications, and strives to use original or license-free graphics and texts.

All brand names and trademarks mentioned in this Preliminary User's Manual, including those protected by a third party, unless specified otherwise in writing, are subjected to the specifications of the current copyright laws and the proprietary laws of the present registered proprietor without any limitation. One should conclude that brand and trademarks are rightly protected by a third party.

#### 1.3 Disclaimer

TQ-Systems GmbH does not guarantee that the information in this Preliminary User's Manual is up-to-date, correct, complete or of good quality. Nor does TQ-Systems GmbH assume guarantee for further usage of the information. Liability claims against TQ-Systems GmbH, referring to material or non-material related damages caused, due to usage or non-usage of the information given in this Preliminary User's Manual, or due to usage of erroneous or incomplete information, are exempted, as long as there is no proven intentional or negligent fault of TQ-Systems GmbH.

TQ-Systems GmbH explicitly reserves the rights to change or add to the contents of this Preliminary User's Manual or parts of it without special notification.

#### 1.4 Imprint

TQ-Systems GmbH Gut Delling, Mühlstraße 2

#### D-82229 Seefeld

Tel: +49 8153 9308-0

Fax: +49 8153 9308-4223

Email: info@tq-group.com

Web: www.tq-group.com/

# 1.5 Service and Support

Please visit our website www.tq-group.com for latest product documentation, drivers, utilities and technical support.

Through our website <u>www.tq-group.com</u> you could also get registered, to have access to restricted information and automatic update services.

For direct technical support you could contact our FAE team by email: <a href="mailto:support@tq-group.com">support@tq-group.com</a>

Our FAE team can support you also with additional information like 3D-STEP files and confidential information which is not provided on our public website.

For service / RMA, please contact our service team by email (service@tq-group.com) or your dedicated sales team at TQ.

# 1.6 Tips on Safety

Improper or incorrect handling of the product can substantially reduce its life span.

#### 1.7 Symbols and Typographic Conventions

Table 1: Terms and Conventions

| Symbol   | Meaning                                                                                                                                                                                                                                                                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | This symbol represents the handling of electrostatic-sensitive modules and / or components. These components are often damaged / destroyed by the transmission of a voltage higher than about 50 V. A human body usually only experiences electrostatic discharges above approximately 3,000 V. |

| 4        | This symbol indicates the possible use of voltages higher than 24 V. Please note the relevant statutory regulations in this regard. Non-compliance with these regulations can lead to serious damage to your health and also cause damage / destruction of the component.                       |

| <u>^</u> | This symbol indicates a possible source of danger. Acting against the procedure described can lead to possible damage to your health and / or cause damage / destruction of the material used.                                                                                                  |

| î        | This symbol represents important details or aspects for working with TQ-products.                                                                                                                                                                                                               |

| Command  | A font with fixed-width is used to denote commands, contents, file names, or menu items.                                                                                                                                                                                                        |

# 1.8 Handling and ESD Tips

# General handling of your TQ-products

The TQ-product may only be used and serviced by certified personnel who have taken note of the information, the safety regulations in this document and all related rules and regulations.

A general rule is: do not touch the TQ-product during operation. This is especially important when switching on, changing jumper settings or connecting other devices without ensuring beforehand that the power supply of the system has been switched off.

Violation of this guideline may result in damage / destruction of the TQMxE41S and be dangerous to your health.

Improper handling of your TQ-product would render the guarantee invalid.

## Proper ESD handling

The electronic components of your TQ-product are sensitive to electrostatic discharge (ESD). Always wear antistatic clothing, use ESD-safe tools, packing materials etc., and operate your TQ-product in an ESD-safe environment. Especially when you switch modules on, change jumper settings, or connect other devices.

#### 1.9 Naming of Signals

A hash mark (#) at the end of the signal name indicates a low-active signal.

Example: RESET#

If a signal can switch between two functions and if this is noted in the name of the signal, the low-active function is marked with a hash mark and shown at the end.

Example: C / D#

If a signal has multiple functions, the individual functions are separated by slashes when they are important for the wiring. The identification of the individual functions follows the above conventions.

Example: WE2# / OE#

#### 1.10 Further Applicable Documents / Presumed Knowledge

#### • Specifications and manual of the modules used:

These documents describe the service, functionality and special characteristics of the module used.

#### • Specifications of the components used:

The manufacturer's specifications of the components used, for example CompactFlash cards, are to be taken note of. They contain, if applicable, additional information that must be taken note of for safe and reliable operation. These documents are stored at TQ-Systems GmbH.

#### • Chip errata:

It is the user's responsibility to make sure all errata published by the manufacturer of each component are taken note of. The manufacturer's advice should be followed.

#### Software behaviour:

No warranty can be given, nor responsibility taken for any unexpected software behaviour due to deficient components.

#### General expertise:

Expertise in electrical engineering / computer engineering is required for the installation and the use of the device.

Implementation information for the carrier board design is provided in the SMARC Design Guide (2) maintained by the SGET (Standardization Group for Embedded Technologies). This Carrier Design Guide includes a very good guideline to design SMARC carrier board.

It includes detailed information with schematics and detailed layout guidelines.

Please refer to the official SGET documentation for additional information (1).

#### 2. INTRODUCTION

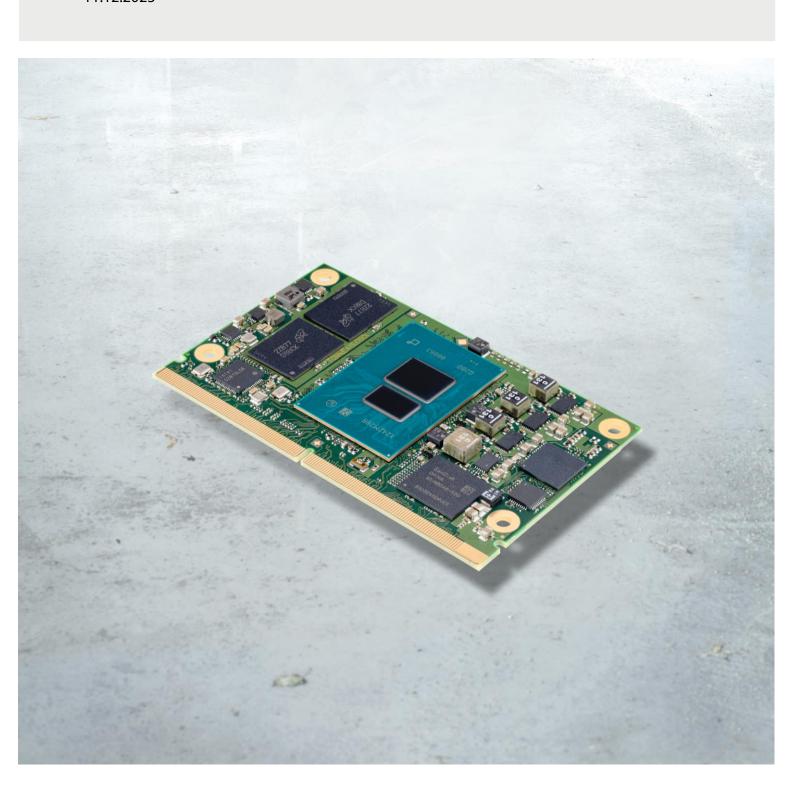

The TQ module TQMxE41S is based on the latest generation of Intel<sup>®</sup> Atom<sup>™</sup>, Pentium<sup>®</sup> and Celeron<sup>®</sup> CPUs (code name "Alder Lake"). It achieves a new level of computing performance, security and media processing performance in a very compact form factor to empower real-time computing, industrial automation, digital surveillance, aviation, medical, retail and more.

The TQMxE41S corresponds to the internationally established SGET standard SMARC (V2.1.1). Six USB ports – including two USB 3.0 – and up to four PCle lanes natively supported by the CPUs enable high bandwidth communication with peripherals and additional interfaces on the carrier board. With the latest Intel® graphics processor integrated, the TQMxE41S delivers 4K high resolution graphics output, immersive 3D processing and also greatly increased video encode and playback performance.

Time coordinated computing capabilities enable time synchronized processes within IoT networks and industrial control applications. On-board eMMC and the option for LVDS or native eDP enable flexibility and reduce overall BOM cost.

The integrated TQMx86 board controller enables high flexibility through "flexiCFG" and supports thermal management, watchdog, 16550 compatible UARTs, I<sup>2</sup>C controllers, and GPIO handling. Combined with options like conformal coating and optimized cooling solutions the TQMxE41S perfectly fits for mobile, low power, low profile and battery driven applications in multiple vertical markets like industrial automation, medical devices, transportation and others.

#### 2.1 Functional Overview

The following key functions are implemented on the TQMxE41S:

#### CPU:

- Intel® x7000 Series and Core i3 N-Series: "Alder Lake N" with different SKUs

- optimized for Embedded, Edge Computing or PC Client applications

#### Memory:

- LPDDR5: 4 Gbyte, 8 Gbyte, 16 Gbyte with up to 4800 MT/s and optional In Band ECC (IBECC)

- eMMC 5.1 on-board flash with up to 256 GB

- EEPROM: 32 kbit

#### **Graphics:**

- 2 × Digital Display Interface (DDI) (2x DP or 1x DP and 1x HDMI)

- ullet 1 imes Embedded Display Port Interface or LVDS interface (eDP or LVDS)

## Peripheral interfaces:

- 2 × 2.5 Gigabit Ethernet (Intel® i226)

- 1 × SATA 3.0 (up to 6 Gb/s)

- 4 × PCle Gen3 (up to 8 GT/s)

- 2 × USB 3.2 (with up to 10Gb/s and USB 2.0 backward compatibility)

- 6 × USB 2.0 (incl. USB 3.2 ports)

- 1 × Intel<sup>®</sup> HD audio (HDA) and I<sup>2</sup>S or 2x I<sup>2</sup>S

- 1 × I<sup>2</sup>C (General Purpose)

- 1 × SMBus

- 1 × SPI (for external uEFI BIOS flash)

- 1 x eSPI interface

- 4 × Serial port (Rx/Tx, legacy compatible)

- 14 GPIO signals (multiplexed with fan / camera control and HD audio Reset)

## **Security components:**

TPM (SLX9670 TPM 2.0)

#### Others:

• TQMx86 board controller with Watchdog and TQ-flexiCFG

# **Power supply:**

Voltage: 4.75 V to 5.25 V3 V Battery for RTC

#### **Environment:**

• Standard Temperature: 0 °C to +60 °C

## Form factor / dimensions:

• SMARC short form factor; 82 mm × 50 mm

# 2.2 SMARC Specification Compliance

The TQMxE41S is compliant to the SMARC Hardware Specification (Version 2.1.1)

#### 2.3 TOMxE41S Variants

The TQMxE41S is available in several standard configurations:

Please visit <u>www.tq-group.com/TQMxE41S</u> for a complete list of standard variants.

Other configurations are available on request.

# Standard configuration features are:

- eDP or LVDS

- 2x DP++ or 1x DP++ and HDMI

- CPU version

- Memory configuration (RAM / eMMC)

- TPM

# Optional hardware and software configuration features:

- Conformal coating can be offered as custom specific add-on

- Custom specific GPIO configuration through TQ-flexiCFG

- Custom specific BIOS configuration

#### 2.4 Accessories

TQMxE41S-HSP: Heat spreader for TQMxE41S according to the SMARC specification Evaluation platform MB-SMARC-3:

- Mainboard for SMARC modules

- 170 mm × 170 mm

- Interfaces:

- o DP++, HDMI 2.0, eDP/LVDS,

- $\circ$  2 × GbE

- o 1 × USB Type C, 1 x USB 3.0, 1 x USB 2.0

- o HDA and I<sup>2</sup>S Audio

- Micro SD card (not applicable with TQMxE41S)

- o 3 x M.2 socket (Key B, E, M), PCle socket

- o up to 6 serial interfaces

- o 2 × CAN (not applicable with TQMxE41S)

# 3. FUNCTION

# 3.1 TQMxE41S Block Diagram

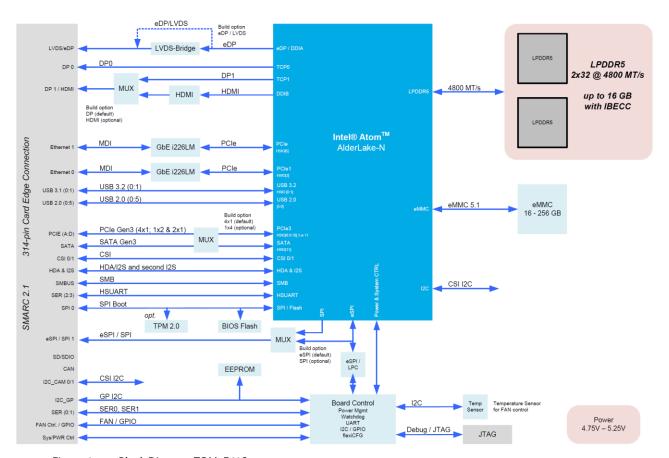

The following illustration shows the block diagram of the TQMxE41S:

Figure 1: Block Diagram TQMxE41S

# 3.2 Electrical Characteristics

# 3.2.1 Supply Voltage

The TQMxE41S supports an input voltage from 4.75 V to 5.25 V.

The following supply voltages are specified at the SMARC connector:

Main Power Rail: 4.75 V to 5.25 V max input ripple: ±100 mV

VCC\_RTC: 2.0 V to 3.3 V max input ripple: ±20 mV

The input voltages shall rise from 10 % of nominal to 90 % of nominal within 0.1 to 20 ms (0.1 ms  $\leq$  Rise Time  $\leq$  20 ms). There must be a smooth and continuous ramp of each DC output voltage from 10 % to 90 % of its final set point within the regulation band.

#### 3.2.2 Power Consumption

The values below show voltage and power consumption details for the TQMxE41S.

The values were measured using the TQMxE41S and the MB-SMARC-3 carrier board.

The measurement was done with two power supplies, one for the TQMxE41S and one for the MB-SMARC-3 carrier board.

The power consumption of each TQMxE41S was measured running Windows $^{\$}$  10, 64 bit and different LPDDR5 configurations. All measurements were done at a temperature of +25  $^{\circ}$ C and an input voltage of +5.0 V.

The power consumption of the TQMxE41S depends on the application, the mode of operation and the operating system.

The power consumption was measured under the following conditions:

#### Suspend mode:

The system is in S5/S4 state, Ethernet ports disconnected.

#### • Windows 10, 64 bit, idle:

Desktop idle, Ethernet ports disconnected.

#### • Windows 10, 64 bit, maximum load:

These values show the maximum worst case power consumption, achieved by using the Intel® stress test tool to apply maximum load to the cores only, and cores plus graphics engine

#### • Windows 10, 64 bit, Suspend Mode:

The system is in S5/S4 state, Ethernet port is disconnected.

The following table shows the power consumption with different CPU configurations.

Table 2: TQMxE41S Power Consumption

| Module                        | Mode                   |                    |                         |  |  |

|-------------------------------|------------------------|--------------------|-------------------------|--|--|

| Module                        | Suspend (OS shut down) | Win10, 64 bit idle | Win10, 64 bit max. load |  |  |

| SKU2 N97 with 8GB LPDDR5      | 0.88 W                 | 4.2 W              | 15W / 17W               |  |  |

| SKU3 N200 with 8GB LPDDR5     | 0.88 W                 | 4.9 W              | 8.5W / 16W              |  |  |

| SKU4 Core-I3 with 16GB LPDDR5 | 0.88 W                 | 4.8 W              | 16W / 18.5 W            |  |  |

| SKU5 x7211E with 4GB LPDDR5   | 0.88 W                 | 5.5 W              | 8.5W / 12.5W            |  |  |

# Note: Power requirement

The power supplies on the carrier board for the TQMxE41S must be designed with enough reserve. The carrier board should provide at least twice the maximum workload power of the TQMxE41S. The TQMxE41S supports several low-power states. The power supply of the carrier board has to be stable even with no load.

# 3.2.2.1 Real Time Clock Power Consumption

The RTC (VCC\_RTC) current consumption is shown below.

The values were measured at +25 °C under battery operating conditions.

Table 3: RTC Current Consumption

| Integrated RTC                                    | Voltage | Current |

|---------------------------------------------------|---------|---------|

| Intel® X7000E and Core i3 N-Series "Alder Lake N" | 3.0 V   | 3 μΑ    |

The current consumption of the RTC in the Intel® X7000E and Core i3 N-Series "Alder Lake N" in the Product Family Datasheet (Electrical an Thermal Specifications) is specified with  $8\mu A$  max at room temperature while the system is off. The values measured on was lower than  $3\mu A$ .

#### 3.3 Environmental conditions

Operating Temperature Standard: 0 °C to +60 °C

Storage Temperature: -40 °C to +85 °C

Relative humidity (operating / storage):

10 % to 90 % (non-condensing)

# Attention: Maximum operating temperature

Do not operate the TQMxE41S without heat spreader or without heat sink! The heat spreader is not a sufficient heat sink!

# 3.4 System Components

# 3.4.1 CPUs

The TQMxE41S supports the Intel® X7000E and Core i3 N-Series.

Table 4: Intel® X7000E Series: Comparison of the SKUs

| Mode                                    | Intel <sup>®</sup><br>Processor<br>N50 | Intel <sup>®</sup><br>Processor<br>N97 | Intel <sup>®</sup><br>Processor<br>N200 |         | rocessor<br>1305 | Intel <sup>®</sup><br>Processor<br>x7211E | Intel <sup>®</sup><br>Processor<br>X7425E | Intel°<br>Processor<br>x7213E |

|-----------------------------------------|----------------------------------------|----------------------------------------|-----------------------------------------|---------|------------------|-------------------------------------------|-------------------------------------------|-------------------------------|

| Use<br>Condition                        | PC-Client                              |                                        |                                         |         |                  |                                           | Embedded                                  |                               |

| CPU Cores                               | 2                                      | 4                                      | 4                                       |         | 8                | 2                                         | 4                                         | 2                             |

| CPU<br>frequency                        | 1.0 GHz                                | 2.0 GHz                                | 1.0 GHz                                 | 0.9 GHz | 1.8 GHz          | 1.0 GHz                                   | 1.5 GHz                                   | 1.7 GHz                       |

| Burst<br>frequency                      | 3.4 GHz                                | 3.6 GHz                                | 3.7 GHz                                 | 3.8     | GHz              | 3.2 GHz                                   | 3.4 GHz                                   | 3.2 GHz                       |

| UHD<br>Graphics<br>(Execution<br>Units) | 16 EUs                                 | 24 EUs                                 | 32 EUs                                  | 32 EUs  |                  | 16 EUs                                    | 24 EUs                                    | 16 EUs                        |

| Thermal<br>Design<br>Power (TDP)        | 6 W                                    | 12 W                                   | 6 W                                     | 9 W     | 15 W             | 6 W                                       | 12 W                                      | 10 W                          |

#### 3.4.2 Graphics

The Intel® X7000E Series CPUs includes an integrated Intel® UHD (Gen 12) graphics accelerator. It provides excellent 2D/3D graphics performance with up to three simultaneous display support.

The following list shows some key features of the Intel  $^{\!8}$  X7000E Series CPUs:

- Graphics Technology (Gen 12 Xe LP) with up to 32 Execution Units

- Max. 3 displays @4K60

- Hardware accelerated video decoding/encoding for MPEG2, H.264, WMV9 (VC-1), JPEG/MJPEG, H.265(HEVC), VP9, AV1

- OpenGL 4.6, DirectX 12.1, Vulkan 1.3 support

- OpenCL 3.0 support

$The TQMxE41S \ supports \ two \ Digital \ Display \ Interface \ (DDI) \ and \ one \ eDP \ or \ LVDS \ interface \ at \ the \ SMARC \ connector.$

Table 5: Maximum Resolution

| Display     | Maximum Display Resolution                   |

|-------------|----------------------------------------------|

| LVDS        | 1920 × 1200 at 60 Hz (dual LVDS bus)         |

| eDP         | 1920x1080@60Hz (for most SKUs)               |

| DP          | 4096 × 2160 at 60 Hz                         |

| HDMI 1.4b   | 1920 × 1080 at 60 Hz / 3840 x 2160 at 30Hz / |

| HDIVII 1.40 | 4096 x 2160 @ 24Hz                           |

#### 3.4.3 Memory

#### 3.4.3.1 LPDDR5 SDRAM

The TQMxE41S supports a memory-down 2x32bit LPDDR5 configuration running at up to 4800 MT/s and optional In Band ECC (IBECC). The maximum memory size is 16 Gbyte. The available memory configuration can be either 4 Gbyte, 8 Gbyte, or 16 Gbyte.

#### 3.4.3.2 eMMC

The TQMxE41S supports up to 256 Gbyte on-board eMMC 5.1 flash.

#### Attention: eMMC OS installation

The on-board eMMC Flash requires pre-configuration via EFI Shell before OS installation (e.g. diskpart utility)

#### 3.4.3.3 SPI Boot Flash

The TQMxE41S provides a 256 Mbit SPI boot flash. It includes the uEFI BIOS. An external SPI boot flash can be used instead of the on-board SPI boot flash.

#### 3.4.3.4 EEPROM

On the TQMxE41S there can be placed a 32 kbit serial EEPROM on the I2C\_GP bus. This feature is optional.

#### 3.4.4 Real Time Clock

The TQMxE41S includes a standard RTC integrated in the Intel® X7000E Series CPU.

#### 3.4.5 Trusted Platform Module

The TQMxE41S supports the Trusted Platform Module (TPM) 2.0 (Infineon SLB9670 controller). Intel® X7000E Series CPU supports also a Firmware Trusted Platform Module (FTPM); this is a Trusted Platform Module 2.0 implementation in firmware. This feature can be configured in the BIOS.

#### 3.4.6 TQ flexible I/O configuration (TQ-flexiCFG)

The module includes a flexible I/O configuration feature, the TQ-flexiCFG.

Using the TQ-flexiCFG feature several I/O interfaces and functions can be configured via a programmable FPGA.

This feature enables the user to integrate special embedded features and configuration options in the TQMxE41S to reduce the carrier board design effort. Here are some examples of the flexible I/O configuration:

- GPIO interrupt configuration

- Interrupt configuration via LPC Serial IRQ

- Serial Port handshake signals via GPIOs

- Integrate additional I/O functions, e.g. additional Serial, I<sup>2</sup>C, PWM controller or special power management configurations

Please contact <a href="mailto:support@tq-group.com">support@tq-group.com</a> for further information about the TQ-flexiCFG.

#### 3.5 Interfaces

#### 3.5.1 PCI Express

The TQMxE41S with Intel® X7000E Series CPU supports a very flexible PCI Express configuration with up four PCI Express Gen3 ports.

With a customized BIOS the PCI Express lanes can be configured as follows:

Table 6: PCI Express Configuration Options

| SM | SMARC™ Port A – D |   |                 | Configuration                                     | Configuration                       |  |    |  |    |  |    |  |   |                                   |                                                   |

|----|-------------------|---|-----------------|---------------------------------------------------|-------------------------------------|--|----|--|----|--|----|--|---|-----------------------------------|---------------------------------------------------|

| Α  | В                 | С | D               | 4 ports x1 Lane                                   | Configuration in the BIOS (default) |  |    |  |    |  |    |  |   |                                   |                                                   |

|    | A C D             |   | D               | 1 Port x2 Lanes + 2 Ports x1 Lane                 | Configuration via custom BIOS       |  |    |  |    |  |    |  |   |                                   |                                                   |

| 1  | A C               |   | A C             |                                                   | АС                                  |  | АС |  | АС |  | АС |  | С | 1 Port x2 Lanes + 1 Port x2 Lanes | Configuration via custom BIOS and assembly option |

| A  |                   |   | 1 Port x4 Lanes | Configuration via custom BIOS and assembly option |                                     |  |    |  |    |  |    |  |   |                                   |                                                   |

## Note: PCIe assembly option

With default PCIe assembly option following configurations cannot be used:

- 1 Port x2 Lanes + 2 Ports x1 Lane

- 1 Port x4 Lanes

With the PCIe x4 assembly option SATA port cannot be used.

#### 3.5.2 Serial ATA

The TQMxE41S supports one SATA Gen3.0 interface which supports up to 6 Gb/s. SATA and PCIe form an assembly option. If SATA is used, the following PCIe configurations cannot be used:

1 Port x2 Lanes + 1 Port x2 Lanes

1 Port x4 Lanes

#### 3.5.3 Gigabit Ethernet

The TQMxE41S provides two Intel® i226 Ethernet controller with up to 2.5 Gb/s speed.

In the SMARC specification (1) there are defined two gigabit Ethernet capable ports. Solutions with 2.5 Gb/s are possible with the TQMxE41S. In this case special attention should be paid on the high-speed routing and on the Ethernet Jack or magnetics selection.

When realizing a 1 Gb/s solution, it should be ensured that the established link is limited to this data rate.

# 3.5.4 Digital Display Interface

The TQMxE41S supports three Display Interfaces at the SMARC connector.

The SMARC Primary Display interface supports either LVDS or eDP as an assembly option.

The SMARC Secondary Display interface (HDMI/DP1) supports DisplayPort or HDMI/DVI with an appropriate level realized on the module.

The SMARC Third Display interface (DP++) supports DisplayPort++ solutions or HDMI/DVI with an appropriate level shifter or retimer on the carrier board.

The TQMxE41S supports the following maximum display resolutions:

- DisplayPort 1.4a up to 4096 × 2304 at 60 Hz

- Embedded DisplayPort 1.4b: Default: up to 1920x1080@60Hz; specific SKU: up to 4096 × 2304 at 60 Hz

- HDMI 1.4b up to 1920 × 1080 at 60 Hz / 3840 x 2160 at 30Hz / 4096 x 2160 @ 24Hz

- HDMI 2.0b (appropriate redriver / retimer on carrier board necessary): 4Kx2K@60Hz

# Note: Assembly option for SMARC Secondary Display interface (HDMI/DP1)

With default Display assembly option the TQMxE41S provides DP++ on this interface.

With the assembly option for HDMI on SMARC Secondary Display interface simple HDMI solutions can be realized on the carrier for SMARC Secondary Display interface:

- a special BIOS is necessary to use this option

- an example is included in SMARC Design Guide (2)

- the HDMI 1.4b capable level shifter on TQMxE41S supports data rates up to 3Gbit/s

Please contact <a href="mailto:support@tg-group.com">support@tg-group.com</a> for further information about the display configuration.

#### 3.5.5 LVDS Interface

The TQMxE41S supports an LVDS interface which is provided through an on-board eDP to LVDS bridge.

The eDP to LVDS bridge supports single or dual LVDS signalling with colour depths of 18 bits per pixel or 24 bits per pixel up to 112 MHz and a resolution up to  $1920 \times 1200 @ 60$  Hz in dual LVDS mode. The LVDS data packing can be configured either in VESA or JEIDA format.

To support panels without EDID ROM, the eDP to LVDS bridge can emulate EDID ROM behaviour avoiding specific changes in system video BIOS.

Please contact <a href="mailto:support@tq-group.com">support@tq-group.com</a> for further information about the LVDS configuration.

#### 3.5.6 USB 2.0 Interfaces

The TQMxE41S supports six USB 2.0 and two USB 3.2 Gen2 ports with data rate up to 10 Gb/s at the SMARC connector. The default setting for the USB SuperSpeed ports is 5 Gb/s (USB 3.2 Gen1).

If USB 3.2 Gen2 (10 Gb/s) transfer mode is required, special attention should be paid on the high-speed routing and losses on the SuperSpeed+ signals when designing a carrier.

#### 3.5.7 USB 3.0 Interfaces

The TQMxE41S supports two SuperSpeed+ ports at the SMARC connector.

## **Note: USB Port Mapping**

The USB 2.0 port 2 must be paired with USB 3.2 SuperSpeed port 2. The USB 2.0 port 3 must be paired with USB 3.2 SuperSpeed port 3.

## 3.5.8 General Purpose Input/Output

The TQMxE41S provides 14 GPIO signals at the SMARC connector. These GPIO signals are shared with camera control, fan Control and HD Audio Reset signals. They can be configured by software.

The GPIO signals are integrated in the TQ-flexiCFG block and can be configured flexible. Therefore the signals can also be used for several special functions (see 3.4.6).

Please contact <a href="mailto:support@tq-group.com">support@tq-group.com</a> for further information about the GPIO configuration and their alternate uses.

#### 3.5.9 Audio Interfaces

The TQMxE41S provides a High Definition Audio (HDA) and an I<sup>2</sup>S interface, which support Audio codecs at the SMARC connector. The audio codec on the carrier board should be supported by the BIOS of the TQMxE41S. The HDA interface can also be used as second I<sup>2</sup>S interface.

Please contact support@tq-group.com for further information regarding configuration and supported codecs.

#### 3.5.10 I<sup>2</sup>C Bus

The TQMxE41S supports a general purpose  $I^2C$  bus via a dedicated LPC to  $I^2C$  controller, integrated in the TQ-flexiCFG block. The  $I^2C$  host controller supports a clock frequency of up to 400 kHz and can be configured independently.

#### 3.5.11 SMBus / Power Management I<sup>2</sup>C Bus

The TQMxE41S provides an I<sup>2</sup>C based System Management Bus (SMBus) interface. This bus is also called Power Management I<sup>2</sup>C Bus.

#### 3.5.12 Serial Peripheral Interface

The TQMxE41S provides an SPI interface. The SPI interface can only be used for SPI boot Flash devices. A second SPI Interface is multiplexed (assembly option) with eSPI Interface.

$Please\ contact\ \underline{support@tq-group.com}\ for\ further\ information\ about\ eSPI\ /\ SPI\ configuration.$

#### 3.5.13 eSPI

The TQMxE41S provides an eSPI interface, which is multiplexed (assembly option) with a second SPI Interface.

Please contact <a href="mailto:support@tq-group.com">support@tq-group.com</a> for further information about eSPI / SPI configuration.

#### 3.5.14 Serial Ports

The TQMxE41S offers up to four UARTs (Universal Asynchronous Receiver and Transmitter). The register set of SER0 and SER1 is based on the industry standard 16550 UART. The UART operates with standard serial port drivers without requiring a custom driver to be installed. The 16 byte transmit and receive FIFOs reduce CPU overhead and minimize the risk of buffer overflow and data loss

SER2 and SER3 are connected to the processor internal UARTs of the Intel® X7000E Series CPU.

#### 3.5.15 Watchdog Timer

The TQMxE41S supports a freely programmable two-stage watchdog timer, integrated in the TQ-flexiCFG block.

There are four operation modes available for the watchdog timer:

- Dual-stage mode

- Interrupt mode

- Reset mode

- Timer mode

The timeout of the watchdog timer ranges from 125 ms to 1 h.

The SMARC specification does not support external hardware triggering of the watchdog. An external watchdog trigger can be configured to GPIO pins at the SMARC connector with the TQ-flexiCFG feature.

#### 3.6 Connectors & LEDs

#### 3.6.1 SMARC Connector

A 314 pin 0.5 mm pitch card edge connector is realized on the TQMxE41S PCB. On the carrier board a connector mechanical compatible to MXM3 graphic cards is used to contact the module. The stacking height is defined by the connector used on the carrier (e.g. 1.5 mm, 2.7 mm, 5 mm, and 8 mm are available).

#### 3.6.2 Debug LED

The TQMxE41S includes a dual colour LED providing boot and BIOS information.

The following table shows some LED boot messages.

Table 7: LED Boot Messages

| Red LED  | Green LED | Remark                     |

|----------|-----------|----------------------------|

| ON       | OFF       | Power supply error         |

| ON       | ON        | S4/S5 state                |

| BLINKING | BLINKING  | S3 state                   |

| OFF      | BLINKING  | uEFI BIOS is booting       |

| OFF      | ON        | uEFI BIOS boot is finished |

#### 3.7 SMARC Connector Pinout

This section describes the TQMxE41S SMARC connector pin assignment, which is compliant with the SMARC hardware specification Version 2.1.1.

# 3.7.1 Signal Assignment Abbreviations

Table 8 lists the abbreviations used in Table 9.

Table 8: Abbreviations used

| Abbreviation | Description                   |

|--------------|-------------------------------|

| GND          | Ground                        |

| PWR          | Power                         |

| 1            | Input                         |

| I PU         | Input with pull-up resistor   |

| I PD         | Input with pull-down resistor |

| 0            | Output                        |

| OD           | Open drain output             |

| IO           | Bi-directional                |

# Note: Unused signals on the carrier board

If the input signals at the SMARC connector are not used, these signals can be left open on the carrier board, since these signals have a termination on the TQMxE41S.

# 3.7.2 SMARC Connector Pin Assignment

Table 9: SMARC Connector Pin Assignment

| P1   SMB ALERT#   SM Bus Alert# (interrupt) signal   IPU   1.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pin | Pin-Signal  | Description                                            | Туре | Level          | Remark   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|--------------------------------------------------------|------|----------------|----------|

| SND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P1  | -           | SM Bus Alert# (interrupt) signal                       | LPU  | 1.8 V          |          |

| P3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | _           |                                                        |      | 1.0 1          | 1        |

| PA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |             |                                                        |      | LVDS D-PHY     |          |

| PS         BEET_SDP         IEEE 1588 Trigger Signal         IO         3.3 V           P6         GBEO_SDP         IEEE 1588 Trigger Signal         IO         3.3 V           P7         CSI1, RNO+         CSI differential data input         I         LVDS D-PHY           P8         CSI, RNO+         CSI differential data input         I         LVDS D-PHY           P0         GND         Ground         GND           P10         CSI, RX1+         CSI differential data input         I         LVDS D-PHY           P12         GSI, RX2+         CSI differential data input         I         LVDS D-PHY           P12         GSI, RX2+         CSI differential data input         I         LVDS D-PHY           P13         CSI, RX2+         CSI differential data input         I         LVDS D-PHY           P13         CSI, RX2+         CSI differential data input         I         LVDS D-PHY           P15         GND         Ground         GND         GND           P16         SSI, RX3+         CSI differential data input         I         LVDS D-PHY           P17         CSI, RX3-         CSI differential data input         I         LVDS D-PHY           P18         GND         GND <t< td=""><td></td><td></td><td></td><td>+</td><td></td><td></td></t<>                                                                                        |     |             |                                                        | +    |                |          |

| RED_SDP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | _           |                                                        | IO   |                |          |

| SSI_RXO+   CSI differential data input   I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | _           | 33 3                                                   | +    |                |          |

| SSI_RX0—   CSI differential data input   I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |             |                                                        | i    |                |          |

| P90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | _           | ·                                                      | i    |                |          |

| P10   CS11_RX1+   CS1 differential data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |             | ·                                                      |      |                |          |

| P11   CSIL_RX1—   CSI differential data input   I LVDS D-PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |             |                                                        |      | LVDS D-PHY     |          |

| P12   GSND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | _           | ·                                                      | 1    |                |          |

| P13   CS1   RX2+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | _           | ,                                                      | GND  |                |          |

| P14   CSI1_RX2—   CSI differential data input   I   LVDS D-PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |             | CSI differential data input                            |      | LVDS D-PHY     |          |

| P15   GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |             | ,                                                      | i    |                |          |

| P16   CS11_RX3+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |             |                                                        | GND  |                |          |

| P17   CS1   RX3 -   CS1   differential data input   I   LVDS D-PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |             |                                                        |      | LVDS D-PHY     |          |

| P18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | _           |                                                        | 1    | ł              |          |

| P19   GBE0_MD13-   Gigabit Ethernet Controller: Media Dependent Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | _           |                                                        | GND  |                |          |