# TQMa62xxL Preliminary User's Manual

TQMa62xxL UM 0001 30.11.2023

# TABLE OF CONTENTS

| 1.                     | ABOUT THIS MANUAL                                 |    |

|------------------------|---------------------------------------------------|----|

| 1.1                    | Copyright and license expenses                    | 1  |

| 1.2                    | Registered trademarks                             | 1  |

| 1.3                    | Disclaimer                                        | 1  |

| 1.4                    | Imprint                                           | 1  |

| 1.5                    | Tips on safety                                    |    |

| 1.6                    | Symbols and typographic conventions               |    |

| 1.7                    | Handling and ESD tips                             |    |

| 1.8                    | Naming of signals                                 |    |

| 1.9                    | Further applicable documents / presumed knowledge |    |

| 2.                     | BRIEF DESCRIPTION                                 |    |

| 3.                     | ELECTRONICS                                       |    |

| 3.1                    | System overview                                   | 5  |

| 3.1.1                  | System architecture / block diagram               |    |

| 3.1.2                  | Functionality                                     |    |

| 3.1.3                  | Pin multiplexing                                  |    |

| 3.2                    | System components                                 | 6  |

| 3.2.1                  | Processor derivatives                             |    |

| 3.2.2                  | Booting                                           | 7  |

| 3.2.2.1                | Boot source                                       |    |

| 3.2.2.2                | Boot device eMMc                                  |    |

| 3.2.2.3                | Boot device NOR-flash                             |    |

| 3.2.3                  | Memory                                            |    |

| 3.2.3.1                | LPDDR4 SDRAM                                      | 9  |

| 3.2.3.2                | eMMC                                              | 9  |

| 3.2.3.3                | NOR-Flash                                         | 10 |

| 3.2.3.4                | EEPROMs                                           | 10 |

| 3.2.4                  | Clock supply                                      | 10 |

| 3.2.5                  | RTC                                               | 11 |

| 3.2.6                  | Secure Element                                    | 12 |

| 3.2.7                  | Temperature sensor                                |    |

| 3.2.8                  | Interfaces                                        |    |

| 3.2.8.1                | GPIO                                              |    |

| 3.2.8.2                | JTAG                                              |    |

| 3.2.8.3                | I <sup>2</sup> C                                  |    |

| 3.2.8.4                | UART                                              |    |

| 3.2.8.5                | EXTINT#                                           |    |

| 3.2.9                  | Reset                                             |    |

| 3.2.9.1                | Reset Options (Input)                             |    |

| 3.2.9.1.1              | TQMa62xxL_HARD_RST#                               |    |

| 3.2.9.1.3              | MCU_PORz                                          |    |

| 3.2.9.1.4              | MCU_RESETz                                        |    |

| 3.2.9.1.5              | RESET_REQz                                        |    |

| 3.2.9.2                | Reset Status (Output)                             |    |

| 3.2.9.2.1<br>3.2.9.2.2 | PORz_OUT<br>MCU_RESETSTATz                        |    |

| 3.2.9.2.3              | RESETSTATZ                                        |    |

| 3.2.9.3                | Control signals                                   |    |

| 3.2.9.3.1              | TQMa62xxL_PGOOD                                   |    |

| 3.2.9.3.2              | VSEL SD                                           |    |

| 3.2.10                 | Watchdog                                          |    |

| 3.2.11                 | Power supply                                      |    |

| 3.2.11.1               | Main power supply                                 |    |

| 3.2.11.2               | Overview TQMa62xxL supply                         |    |

| 3.2.11.3               | Power sequenzing                                  |    |

| 3.2.11.4               | Power modes                                       |    |

| 3.2.11.5               | Power consumption                                 |    |

| 3.3                    | TQMa62xxL interface                               |    |

| 3.3.1                  | Pin assignment                                    | 18 |

| 3.3.2                  | Pinout TQMa62xxL                                  | 20 |

| 4                      | SOFTWARE                                          | 38 |

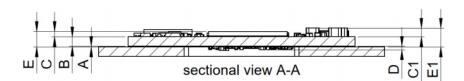

| 5.    | MECHANICS                                      | 39 |

|-------|------------------------------------------------|----|

| 5.1   | TQMa62xxL dimensions and footprint             | 39 |

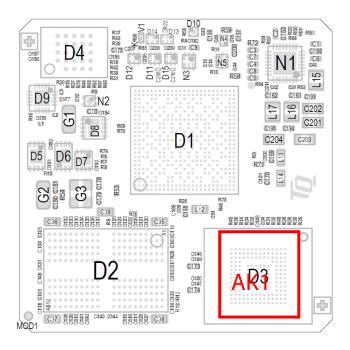

| 5.2   | TQMa62xxL component placement and labeling     | 40 |

| 5.3   | Protection against external effects            | 40 |

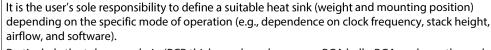

| 5.4   | Thermal management                             | 40 |

| 5.5   | Structural requirements                        | 41 |

| 5.    | SAFETY REQUIREMENTS AND PROTECTIVE REGULATIONS | 42 |

| 5.1   | EMC                                            | 42 |

| 5.2   | ESD                                            | 42 |

| 5.3   | Operational safety and personal security       | 42 |

| 5.4   | Climatic and operational conditions            | 42 |

| 5.5   | Intended Use                                   |    |

| 5.6   | Export Control and Sanctions Compliance        | 43 |

| 5.7   | Warranty                                       | 43 |

| 5.8   | Reliability and service life                   | 43 |

| 5.9   | Environment protection                         | 43 |

| 5.9.1 | RoHS                                           | 43 |

| 5.9.2 | WEEE <sup>®</sup>                              | 43 |

| 5.10  | REACH®                                         | 43 |

| 5.11  | EuP                                            | 44 |

| 5.12  | Statement on California Proposition 65         | 44 |

| 5.13  | Battery                                        |    |

| 5.14  | Packaging                                      | 44 |

| 5.15  | Other entries                                  | 44 |

| 7.    | APPENDIX                                       | 45 |

| 7.1   | Acronyms and definitions                       | 45 |

| 7.2   | References                                     | 47 |

# **TABLE DIRECTORY**

| Table 1:  | Terms and Conventions                                           | 2  |

|-----------|-----------------------------------------------------------------|----|

| Table 2:  | AM62x derivatives (Source: Texas Instruments)                   | 6  |

| Table 3:  | Selecting the General Boot Configuration                        | 7  |

| Table 4:  | Boot device selection eMMC                                      | 8  |

| Table 5:  | Selection of the boot device NOR flash                          | 8  |

| Table 6:  | eMMC Flash modes                                                | 9  |

| Table 7:  | NOR-Flash modes                                                 | 10 |

| Table 8:  | JTAG signals                                                    | 13 |

| Table 9:  | I2C address assignment on the module                            | 13 |

| Table 10: | I2C address assignment on the moduleSupply voltages             | 16 |

| Table 11: | Current consumption TOMa62xx                                    | 18 |

| Table 12: | Pinout                                                          | 20 |

| Table 13: | Climate and operational conditions industrial temperature range |    |

| Table 14: | Acronyms                                                        | 45 |

| Table 15: | Further applicable documents                                    |    |

# FIGURE DIRECTORY

| Figure 1:  | Block diagram AM62x                                                                                   | ∠  |

|------------|-------------------------------------------------------------------------------------------------------|----|

| Figure 2:  | Block diagram TQMa62xxLBlock diagram boot strapping                                                   | 5  |

| Figure 3:  | Block diagram boot strapping                                                                          | 7  |

| Figure 4:  | Block diagram DDR3L SDRAM connection                                                                  | 9  |

| Figure 5:  | Block diagram DDR3L SDRAM connection<br>Block diagram eMMC flash interface<br>Block diagram NOR-Flash | 9  |

| Figure 6:  | Block diagram NOR-Flash                                                                               | 10 |

| Figure 7:  | Block diagram clock supply<br>Block diagram RTC<br>Block diagram SEC                                  | 10 |

| Figure 8:  | Block diagram RTC                                                                                     | 11 |

| Figure 9:  | Block diagram SEC                                                                                     | 12 |

| Figure 10: | Block diagram JTAG                                                                                    | 12 |

| Figure 11: | Block diagram I2C bus on the TQMa62xx                                                                 | 13 |

| Figure 12: | Block diagram Reset                                                                                   | 14 |

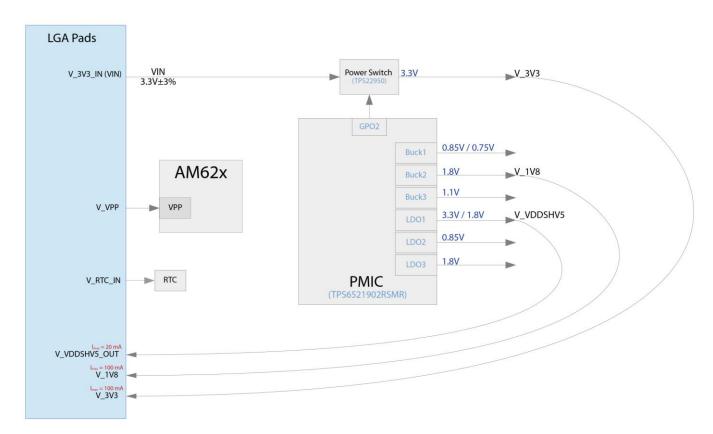

| Figure 13: | Block diagram power supply                                                                            | 16 |

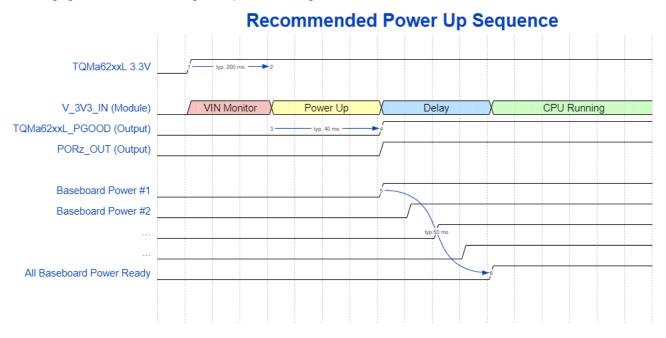

| Figure 14: | Recommended power up sequence                                                                         | 17 |

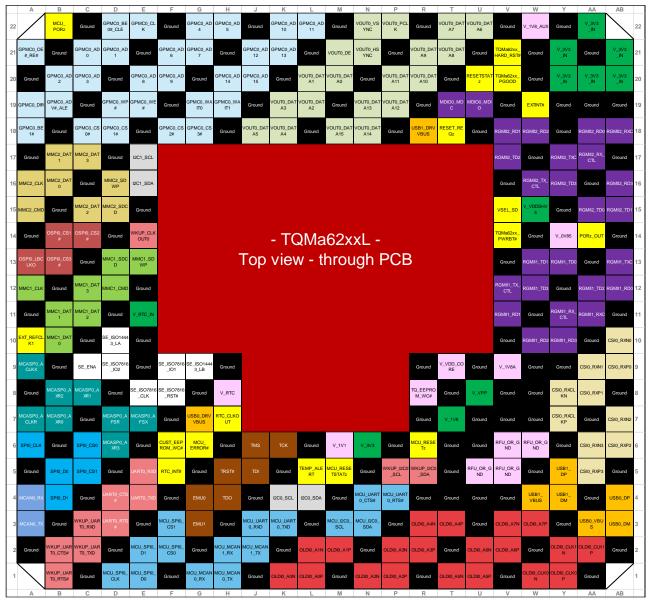

| Figure 15: | Pad placement                                                                                         | 19 |

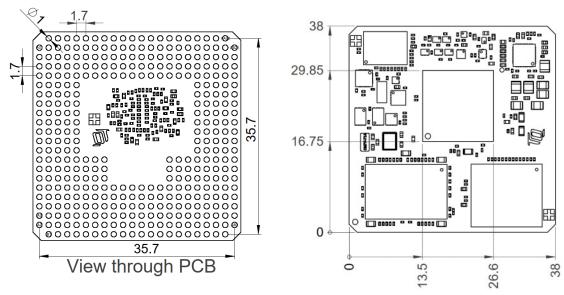

| Figure 16: | Dimensions TQMa62xxL                                                                                  | 39 |

| Figure 17: | TOMa62xxL top view                                                                                    | 40 |

# **REVISION HISTORY**

| Rev. | Date       | Name       | Pos. | Modification    |

|------|------------|------------|------|-----------------|

| 0001 | 30.11.2023 | M. Kreuzer | All  | Initial release |

#### 1. ABOUT THIS MANUAL

#### 1.1 Copyright and license expenses

Copyright protected © 2023 by TQ-Systems GmbH.

This Preliminary User's Manual may not be copied, reproduced, translated, changed or distributed, completely or partially in electronic, machine readable, or in any other form without the written consent of TQ-Systems GmbH.

The drivers and utilities for the components used as well as the BIOS are subject to the copyrights of the respective manufacturers. The licence conditions of the respective manufacturer are to be adhered to.

Bootloader-licence expenses are paid by TQ-Systems GmbH and are included in the price.

Licence expenses for the operating system and applications are not taken into consideration and must be calculated / declared separately.

#### 1.2 Registered trademarks

TQ-Systems GmbH aims to adhere to copyrights of all graphics and texts used in all publications, and strives to use original or license-free graphics and texts.

All brand names and trademarks mentioned in this Preliminary User's Manual, including those protected by a third party, unless specified otherwise in writing, are subjected to the specifications of the current copyright laws and the proprietary laws of the present registered proprietor without any limitation. One should conclude that brand and trademarks are rightly protected by a third party.

#### 1.3 Disclaimer

TQ-Systems GmbH does not guarantee that the information in this Preliminary User's Manual is up-to-date, correct, complete or of good quality. Nor does TQ-Systems GmbH assume guarantee for further usage of the information. Liability claims against TQ-Systems GmbH, referring to material or non-material related damages caused, due to usage or non-usage of the information given in this Preliminary User's Manual, or due to usage of erroneous or incomplete information, are exempted, as long as there is no proven intentional or negligent fault of TQ-Systems GmbH.

TQ-Systems GmbH explicitly reserves the rights to change or add to the contents of this Preliminary User's Manual or parts of it without special notification.

# **Important Notice:**

Before using the Starterkit MBa62xx or parts of the schematics of the MBa62xx, you must evaluate it and determine if it is suitable for your intended application. You assume all risks and liability associated with such use. TQ-Systems GmbH makes no other warranties including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. Except where prohibited by law, TQ-Systems GmbH will not be liable for any indirect, special, incidental or consequential loss or damage arising from the usage of the Starterkit MBa62xx or schematics used, regardless of the legal theory asserted.

## 1.4 Imprint

TQ-Systems GmbH Gut Delling, Mühlstraße 2

# D-82229 Seefeld

Tel: +49 8153 9308–0

Fax: +49 8153 9308–4223

E-Mail: Info@TQ-Group

Web: TQ-Group

#### 1.5 Tips on safety

Improper or incorrect handling of the product can substantially reduce its life span.

# 1.6 Symbols and typographic conventions

Table 1: Terms and Conventions

| Symbol    | Meaning                                                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | This symbol represents the handling of electrostatic-sensitive devices and / or components. These components are often damaged / destroyed by the transmission of a voltage higher than about 50 V.  A human body usually only experiences electrostatic discharges above approximately 3,000 V. |

| 4         | This symbol indicates the possible use of voltages higher than 24 V.  Please note the relevant statutory regulations in this regard.  Non-compliance with these regulations can lead to serious damage to your health and also cause damage / destruction of the component.                      |

| <u>^</u>  | This symbol indicates a possible source of danger. Acting against the procedure described can lead to possible damage to your health and / or cause damage / destruction of the material used.                                                                                                   |

| <u>^i</u> | This symbol represents important details or aspects for working with TQ-products.                                                                                                                                                                                                                |

| Command   | A font with fixed-width is used to denote commands, file names, or menu items.                                                                                                                                                                                                                   |

# 1.7 Handling and ESD tips

# General handling of your TQ-products

The TQ-product may only be used and serviced by certified personnel who have taken note of the information, the safety regulations in this document and all related rules and regulations.

A general rule is: do not touch the TQ-product during operation. This is especially important when switching on, changing jumper settings or connecting other devices without ensuring beforehand that the power supply of the system has been switched off.

Violation of this guideline may result in damage / destruction of the TQMa62xxL and be dangerous to your health.

Improper handling of your TQ-product would render the guarantee invalid.

## Proper ESD handling

The electronic components of your TQ-product are sensitive to electrostatic discharge (ESD). Always wear antistatic clothing, use ESD-safe tools, packing materials etc., and operate your TQ-product in an ESD-safe environment. Especially when you power up the TQMa62xxL or the Starterkit, change jumper settings, or connect other devices.

#### 1.8 Naming of signals

A hash mark (#) at the end of the signal name indicates a low-active signal.

Example: RESET#

If a signal can switch between two functions and if this is noted in the name of the signal, the low-active function is marked with a hash mark and shown at the end.

Example: C / D#

If a signal has multiple functions, the individual functions are separated by slashes when they are important for the wiring. The identification of the individual functions follows the above conventions.

Example: WE2# / OE#

#### 1.9 Further applicable documents / presumed knowledge

#### • Specifications and manuals of the modules used:

These documents describe the service, functionality and special characteristics of the module used (incl. BIOS).

#### • Specifications of the components used:

The manufacturer's specifications of the components used, for example CompactFlash cards, are to be taken note of. They contain, if applicable, additional information that must be taken note of for safe and reliable operation. These documents are stored at TQ-Systems GmbH.

#### Chip errata:

It is the user's responsibility to make sure all errata published by the manufacturer of each component are taken note of. The manufacturer's advice should be followed.

#### • Software behaviour:

No warranty can be given, nor responsibility taken for any unexpected software behaviour due to deficient components.

# • General expertise:

Expertise in electrical engineering / computer engineering is required for the installation and the use of the device.

The following documents are required to fully comprehend the following contents:

- MBa62xx circuit diagram

- MBa62xx User's Manual

- Sitara™ AM62x Data Sheet

• U-Boot documentation: <u>www.denx.de/wiki/U-Boot/Documentation</u>

• PTXdist documentation: <u>www.ptxdist.de</u>

• TQ-Support Wiki: <a href="mailto:support.tq-group.com/doku.php?id=en:arm:tqmax62xx">support.tq-group.com/doku.php?id=en:arm:tqmax62xx</a>

# 2. BRIEF DESCRIPTION

The TQMa62xxL is a universal TQ-LGA mini module based on the TI Sitara family AM62x with ARM Cortex A53 and Cortex M4F cores.

This Preliminary User's Manual describes the hardware of the TQMa62xxL Rev.010x and refers to some software settings. It does not replace the AM62x Reference Manual (2).

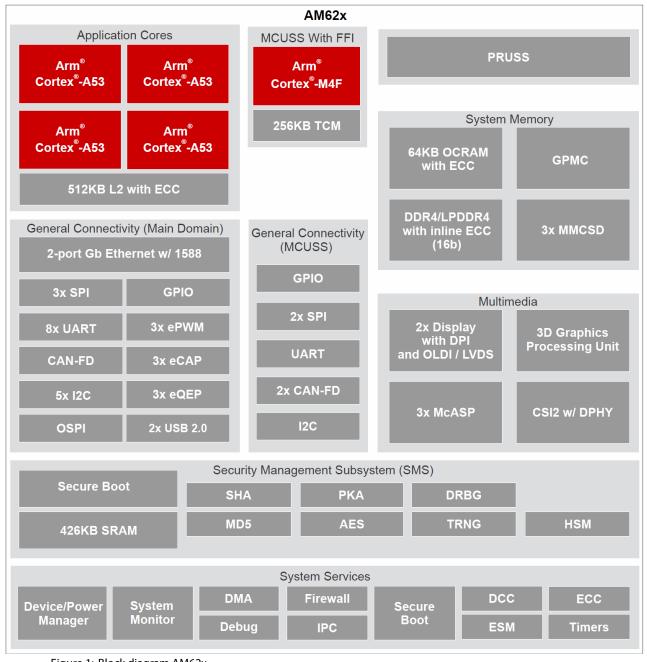

Figure 1: Block diagram AM62x (Source: <u>Texas Instruments</u>)

All useful AM62x signals are routed to the TQMa62xxL LGA pads. There are no restrictions for customers using the TQMa62xxL with respect to an integrated customised design.

Please take note of that not all interfaces can be used simultaneously.

# 3. **ELECTRONICS**

The information provided in this User's Manual is only valid in connection with the tailored boot loader, which is preinstalled on the TQMa62xxL, and the BSP provided by TQ-Systems GmbH, see also section 4.

#### 3.1 System overview

#### 3.1.1 System architecture / block diagram

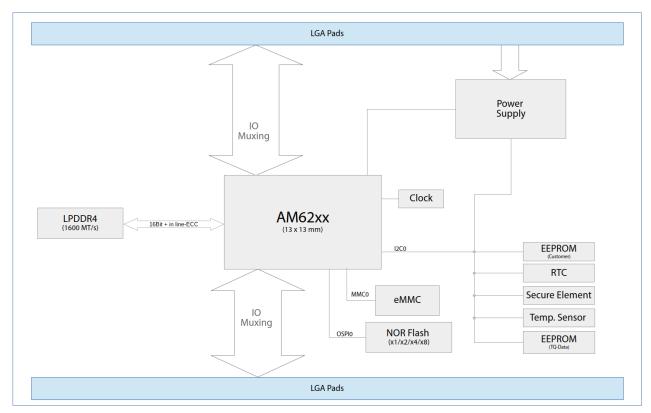

Figure 2: Block diagram TQMa62xxL

# 3.1.2 Functionality

The following key functions are implemented on the TQMa62xxL:

- Mini module with form factor 38 mm x 38 mm

- AM62x CPU (up to 4 x A53 and/ 1 x M4F)

- 16-bit LPDDR4 memory

- 1x eMMC NAND-Flash 5.1

- 1x QSPI-NOR-Flash (optional)

- Clock supply

- EEPROM (optional)

- Real-time clock (optional)

- Secure Element chip (optional)

- Temperature sensor (optional)

- EEPROM (TQ-Data)

- Supervisor

- Single Power Supply 3.3 V

- Availability of all essential signals of the CPU at the LGA pads

# 3.1.3 Pin multiplexing

The pin multiplexing of the AM62x permits to use many pins for different interfaces. The information provided in this User's Manual is based on the <u>BSP provided by TQ-Systems GmbH</u>.

# Attention: Destruction or malfunction

Many AM62x pins can be configured as different function.

Please take note of the information in the AM62 data sheet (1) concerning the configuration of these pins before integration / start-up of your carrier board / Starter kit.

Please also take note of the latest AM62x errata (3).

## 3.2 System components

#### 3.2.1 Processor derivatives

Depending on the TQMa62xxL version, one of the following AM62x derivatives is assembled:  $AM6254 \,/\, AM6252 \,/\, AM6251 \,/\, AM6234 \,/\, AM6232 \,/\, AM6231$

Table 2: AM62x derivatives (Source: Texas Instruments)

| EEATUREO                                                                             | REFERENCE          | AM625                                                    |                          | AM623           |                          |                          |             |

|--------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------|--------------------------|-----------------|--------------------------|--------------------------|-------------|

| FEATURES                                                                             | NAME               | AM6254                                                   | AM6252                   | AM6251          | AM6234                   | AM6232                   | AM6231      |

| CTRLMMR_WKUP_JTAG_DEVICE_ID[31:13] DEVICE_ID register bit field value <sup>(1)</sup> |                    | C: 0x1D123<br>G: 0x1D127                                 | C: 0x1D0A3<br>G: 0x1D0A7 | G: 0x1D067      | C: 0x1D103<br>G: 0x1D107 | C: 0x1D083<br>G: 0x1D087 | G: 0x1D047  |

| PROCESSORS AND ACCELERATORS                                                          | }                  | •                                                        |                          | •               |                          |                          |             |

| Speed Grades (See Table 7-1)                                                         |                    |                                                          |                          | T, S,           | K, G                     |                          |             |

| Arm Cortex-A53<br>Microprocessor Subsystem                                           | Arm A53            | Quad Core                                                | Dual Core                | Single Core     | Quad Core                | Dual Core                | Single Core |

| Arm Cortex-M4F in MCU domain                                                         | Arm M4F            | Single Core<br>Functional Safety Optional <sup>(5)</sup> |                          |                 |                          |                          |             |

| 3D Graphics Engine (OpenGL ES 3.1,<br>Vulkan 1.2)                                    | 3D Graphics engine | Yes                                                      | Yes                      | Yes             | No                       | No                       | No          |

| Device Management Subsystem                                                          | WKUP_R5F           |                                                          |                          | Single          | e core                   |                          |             |

| Crypto Accelerators                                                                  | Security           |                                                          |                          | Y               | es                       |                          |             |

| PROGRAM AND DATA STORAGE                                                             |                    |                                                          |                          |                 |                          |                          |             |

| On-Chip Shared Memory (RAM) in MAIN Domain                                           | OCSRAM             |                                                          |                          | 64KB (with S    | ECDED ECC)               |                          |             |

| On-Chip Shared Memory (RAM) in M4F<br>Domain                                         | MCU_MSRAM          |                                                          |                          | 256             | 6KB                      |                          |             |

| DDR4/LPDDR4 DDR Subsystem                                                            | DDRSS              | 16-l                                                     | oit data with inline     | e ECC; up to 8G | B using DDR4 or          | 4GB using LPD            | DR4         |

| General-Purpose Memory Controller                                                    | GPMC               |                                                          |                          | Up to 1GE       | with ECC                 |                          |             |

| PERIPHERALS                                                                          |                    |                                                          |                          |                 |                          |                          |             |

| Display Subsystem                                                                    | DSS                | 1x DPI<br>1x LVDS                                        |                          |                 |                          |                          |             |

| Modular Controller Area Network<br>Interface with Full CAN-FD Support                | MCAN               | 3                                                        |                          |                 |                          |                          |             |

| General-Purpose I/O                                                                  | GPIO               |                                                          |                          | Up to           | 170                      |                          |             |

| Inter-Integrated Circuit Interface                                                   | I2C                |                                                          |                          | (               | 6                        |                          |             |

| Multichannel Audio Serial Port                                                       | MCASP              |                                                          |                          | ;               | 3                        |                          |             |

| Multichannel Serial Peripheral Interface                                             | MCSPI              |                                                          |                          | !               | 5                        |                          |             |

| Multi-Media Card/ Secure Digital<br>Interface                                        | MM/CSD             |                                                          |                          |                 | C (8-bits)               |                          |             |

| Flash Subsystem (FSS) <sup>(2)</sup>                                                 | OSPI0/QSPI0        |                                                          |                          |                 | s <sup>(2)</sup>         |                          |             |

| Programmable Real-Time Unit Subsystem <sup>(3)</sup>                                 | PRUSS              |                                                          |                          | 2x PRU Cor      | es (Optional)            |                          |             |

| Industrial Communication Subsystem Support <sup>(4)</sup>                            | PRUSS              |                                                          |                          | N               | lo                       |                          |             |

| Gigabit Ethernet Interface                                                           | CPSW3G             |                                                          |                          | Y               | es                       |                          |             |

| General-Purpose Timers                                                               | TIMER              | 12 (4 in MCU Channel)                                    |                          |                 |                          |                          |             |

| Enhanced Pulse-Width Modulator<br>Module                                             | EPWM               | 3                                                        |                          |                 |                          |                          |             |

| Enhanced Capture Module                                                              | ECAP               | 3                                                        |                          |                 |                          |                          |             |

| Enhanced Quadrature Encoder Pulse<br>Module                                          | EQEP               | 3                                                        |                          |                 |                          |                          |             |

| Universal Asynchronous Receiver and<br>Transmitter                                   | UART               | 9                                                        |                          |                 |                          |                          |             |

| CSI2-RX Controller with DPHY                                                         | CSI-RX             | 1                                                        |                          |                 |                          |                          |             |

| USB2.0 Controller with PHY                                                           | USB 2.0            | 2                                                        |                          |                 |                          |                          |             |

#### 3.2.2 Booting

#### 3.2.2.1 Boot source

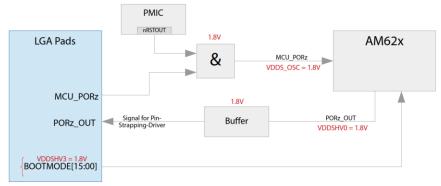

The boot source is selected via the boot strapping pins of the AM62x. The signals are directly routed to the module connectors and will be available again as GPIO after reading the boot configuration.

After the release of MCU\_PORz the boot configuration is read in at the BOOTMODE[15:0] pins. Independent of the boot device, the ROM bootloader is executed first, which assists in reading and executing the application code. The data can be read and loaded either directly from the memory device or by a peripheral.

The following figure shows the implementation of boot strapping on the module:

Figure 3: Block diagram boot strapping

According to the Reference Manual (2) the general boot configuration at the TQMa62xxL can be set as follows:

Table 3: Selecting the General Boot Configuration

| Boot configuration pin | Setting                                                    | TQMa62xxL  |

|------------------------|------------------------------------------------------------|------------|

| BOOTMODE[15:14]        | Reserved, fixed to 0                                       | 00         |

| BOOTMODE[13:10]        | Select the backup boot mode, if primary boot device failed | Don't care |

| BOOTMODE[9:3]          | See following chapters for boot devices                    | -          |

|                        | Ref Clock Select:                                          |            |

|                        | 000 = 19.2 MHz                                             |            |

|                        | 001 = 20 MHz                                               |            |

|                        | 010 = 24 MHz                                               |            |

| BOOTMODE[2:0]          | 011 = 25 MHz                                               | 011        |

|                        | 100 = 26 MHz<br>101 = 27 MHz                               |            |

|                        |                                                            |            |

|                        | 110 = Reserved                                             |            |

|                        | 111 = Reserved                                             |            |

#### **Attention: Malfunction**

All BOOTMODE[15:00] signals must have either a pullup (to  $V_1V8$ ) or pulldown (to Ground). Undefined levels can lead to a malfunction during booting.

# 3.2.2.2 Boot device eMMc

Table 4: Boot device selection eMMC

| Boot configuration pin | Setting                          | TQMa62xxL |

|------------------------|----------------------------------|-----------|

| BOOTMODE[9]            | Port: MMCSD Port 0 (8 bit width) |           |

| BOOTMODE[9]            | This bit must be set to 0        |           |

| BOOTMODE[8]            | Reserved                         | 000       |

| BOOTMODE[7]            | 0 = Filesystem Mode              |           |

| BOOTMODE[7]            | 1 = Raw Mode                     |           |

|                        | Primary Boot Mode:               |           |

|                        | 0000 = Reserved                  |           |

|                        | 0001 = OSPI                      |           |

|                        | 0010 = QSPI                      |           |

|                        | 0011 = SPI                       |           |

|                        | 0100 = Ethernet RGMII            |           |

|                        | 0101 = Ethernet RMII             |           |

|                        | 0110 = I2C                       |           |

| BOOTMODE[6:3]          | 0111 = UART                      | 1000      |

|                        | 1000 = MMCSD boot                |           |

|                        | 1001 = eMMC                      |           |

|                        | 1010 = USB                       |           |

|                        | 1011 = GPMC NAND                 |           |

|                        | 1100 = GPMC NOR                  |           |

|                        | 1101 = PCle                      |           |

|                        | 1110 = xSPI                      |           |

|                        | 1111 = No-boot/Dev boot          |           |

# 3.2.2.3 Boot device NOR-flash

Table 5: Selection of the boot device NOR flash

| Boot configuration pin | Setting                  | TQMa62xxL  |

|------------------------|--------------------------|------------|

| BOOTMODE9              | Reserved, fixed to 0     | Don't Care |

|                        | SPI mode:                |            |

| BOOTMODE8              | 0 = SPI Mode 0           | 1          |

|                        | 1 = SPI Mode 3           |            |

|                        | Chip-Select:             |            |

| BOOTMODE7              | 0 = Boot-Flash is on CS0 | 0          |

|                        | 1 = Boot-Flash is on CS1 |            |

|                        | Primary Boot Mode:       |            |

|                        | 0000 = Reserved          |            |

|                        | 0001 = OSPI              |            |

|                        | 0010 = QSPI              |            |

|                        | 0011 = SPI               |            |

|                        | 0100 = Ethernet RGMII    |            |

|                        | 0101 = Ethernet RMII     |            |

|                        | 0110 = I2C               |            |

| BOOTMODE[6:3]          | 0111 = UART              | 0011       |

|                        | 1000 = MMCSD card        |            |

|                        | 1001 = eMMC              |            |

|                        | 1010 = USB               |            |

|                        | 1011 = GPMC NAND         |            |

|                        | 1100 = GPMC NOR          |            |

|                        | 1101 = PCle              |            |

|                        | 1110 = xSPI              |            |

|                        | 1111 = No-boot/Dev boot  |            |

Further boot configurations can be found in the Reference Manual (2).

Besides the mentioned boot configurations above, it is recommended to consider an alternative boot source during development, e.g. USB boot or no-boot mode for JTAG debug.

# Note: Update

When designing a mainboard, it is recommended to plan a redundant update concept for software updates in the field. Furthermore, it is recommended to switch the conversion of the boot strap pins to high impedance after reading in.

#### 3.2.3 Memory

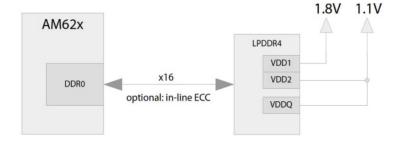

#### 3.2.3.1 LPDDR4 SDRAM

The TQMa62xxL has an LPDDR4 memory with the use of in-line ECC:

- 16-bit bus width with optional ECC (8-bit data + 8-bit ECC)

- Up to 1600 Mbps = 800 MHz

- 1 GByte (=8 Gbit) / 2 GByte (=16 Gbit)

Figure 4: Block diagram DDR3L SDRAM connection

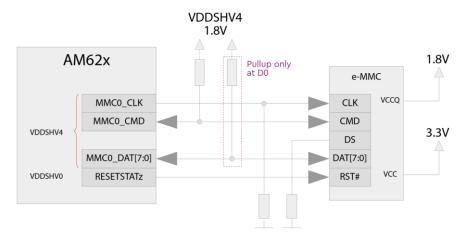

#### 3.2.3.2 eMMC

An eMMC is available to the TQMa62xxL as non-volatile data memory for programs and data (e.g. boot loader, operating system). The used MMC0 signals are not available to the Pinout.

- MMC0 Interface is connected to the eMMC Flash

- 8 / 16 / 32 / 64 GByte

Figure 5: Block diagram eMMC flash interface

The TQMa62xxL supports the following transmission modes:

Table 6: eMMC Flash modes

| Mode          | 1-bit | 4-bit | 8-bit | Note                         |

|---------------|-------|-------|-------|------------------------------|

| Default Speed | n/a   | n/a   | n/a   |                              |

| High Speed    | n/a   | n/a   | Yes   | Boot process                 |

| HS200         | n/a   | n/a   | Yes   | U-boot / Linux               |

| HS400         | n/a   | n/a   | n/a   | MMCSD not supported features |

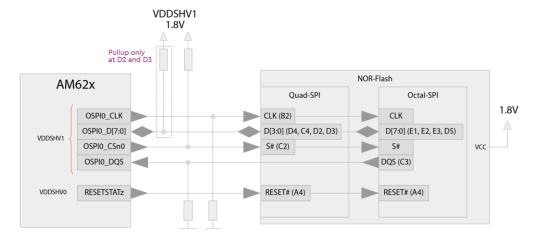

#### 3.2.3.3 NOR-Flash

A NOR-Flash on the TQMa62xxL is available as non-volatile memory. The used OSPI0 signals are not available to the pinout.

- OSPI0 Interface is connected to the NOR Flash

- The NOR-Flash variants Quad SPI Flash and Octal SPI Flash are usable

- 512 / 1024 / 2048 Mbit

Figure 6: Block diagram NOR-Flash

The NOR-Flash variants Quad SPI Flash and Octal SPI Flash are usable. The TQMa62xxL supports the following transmission modes:

Table 7: NOR-Flash modes

| Mode               | Read  | Write | Note                   |

|--------------------|-------|-------|------------------------|

| Extended SPI (SDR) | 1-4-4 | 1-4-4 | Clock = max. 83.33 MHz |

#### 3.2.3.4 EEPROMs

I<sup>2</sup>C EEPROMs are provided on the TQMa62xxL for non-volatile storage. A distinction is made here between:

- Customer data, freely accessible

- TQ manufacturing data ( Serial Number, MAC, ...)

All I<sup>2</sup>C slave address and bus structure are summarized in chapter 3.2.8.3.

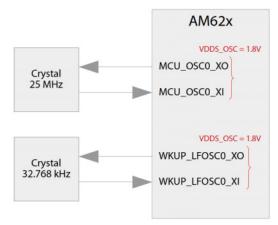

# 3.2.4 Clock supply

The clock supply of the TQMa62xxL is represented as follows:

Figure 7: Block diagram clock supply

To get the module executable only with a 3.3 V supply, MCU\_OSCO\_XO / XI and WKUP\_LFOSC\_XO / XI were implemented as clock on the module. The remaining clock inputs can either be derived from the system clock or fed externally via the module connectors, as an example the following clocks can be fed externally:

- EXT\_REFCLK1

- MCU\_EXT\_REFCLK0 (optional external System Clock inputs)

- CPTS0\_RFT\_CLK (optional CPTS Reference Clock input)

- AUDIO\_EXT\_REFCLKO/1 (optional, External Clock input to McASP)

Further information can be obtained from the associated data sheets (1).

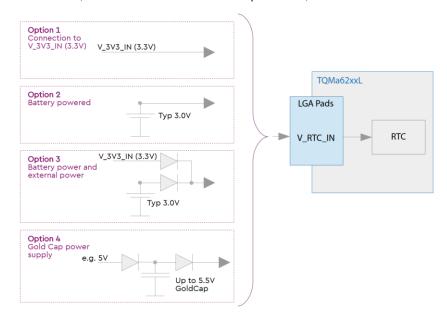

#### 3.2.5 RTC

An optional RTC (NXP PCF85063A) can be equipped on the TQMa62xx. The connection is realized as follows:

- The RTC can be supplied from the base board via V\_RTC\_IN. V\_RTC\_IN = 2.0 V to 5.5V

- RTC\_INT# and RTC\_CLKOUT is accessible at the module connectors.

- RTC\_CLKOUT is only activated as soon as the TQMa62xxL is supplied with V\_3V3\_IN.

- I2C is connected via I2C0 (I<sup>2</sup>C addresses are described in chapter 3.2.8.3)

Figure 8: Block diagram RTC

# Note: Equipping the base board

The RTC is supplied internally by a LDO (1.8V) via V\_RTC\_IN. This allows the user an easy use of Gold-Caps or Coin cells on the main board.

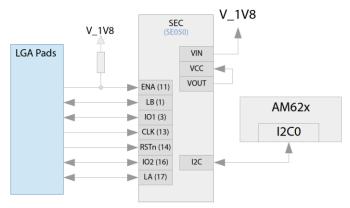

#### 3.2.6 Secure Element

A Secure Element Chip can optionally be fitted on the TQMa62xx. The connection can be seen in the following figure:

Figure 9: Block diagram SEC

The SE050E2HQ1/Z01Z3 from NXP is used as the secure element. All I<sup>2</sup>C addresses are described in chapter 3.2.8.3.

# 3.2.7 Temperature sensor

A temperature sensor (TI TMP1075DSGR) is placed on the TQMa62xxL to monitor the module temperature. The over temperature output (TEMP\_ALERT) of the sensor is available at the module connectors as an open drain output. The  $I^2C$  addresses are described in chapter 3.2.8.3.

#### 3.2.8 Interfaces

In general, except for the memory connection, all IO pins of the CPU are provided at the module connectors. For further information about the interfaces and the pin multiplexing refer to the CPU Reference Manual (2).

# 3.2.8.1 GPIO

Besides their interface function, most AM62x pins can also be used as GPIOs. Details are to be taken from the AM62x Data Sheet (1).

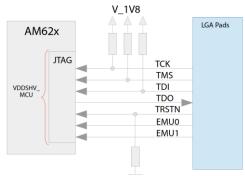

### 3.2.8.2 JTAG

The CPU has a JTAG interface that is directly accessible at the module connectors. The following default configuration is provided on the TQMa62xxL:

Figure 10: Block diagram JTAG

The following table shows the signals used by the JTAG interface.

Table 8: JTAG signals

| Signal / Multiplexing | I/O | Power domain       | Note                                    |

|-----------------------|-----|--------------------|-----------------------------------------|

| TCK                   | 1   | VDDSHV_MCU (1,8 V) | 10 kΩ Pull-up on module                 |

| TDI                   | 1   |                    | 10 kΩ Pull-up on module                 |

| TDO                   | OZ  |                    | Three-state output                      |

| TMS                   | 1   |                    | 10 kΩ Pull-up on module                 |

| TRST#                 | 1   |                    | 4.7 k $\Omega$ Pull-up on module        |

| EMU[1:0]              | Ю   |                    | Optional signals, not required for JTAG |

For more information please refer to the Reference Manual (2).

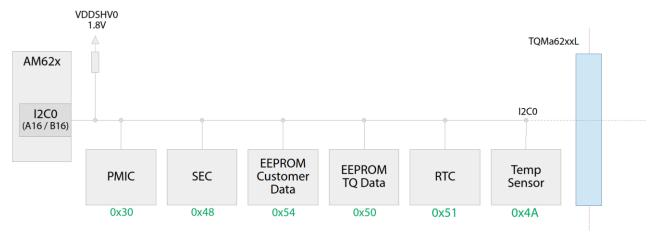

# 3.2.8.3 I<sup>2</sup>C

The accessible  $I^2C$  buses depend on the pin multiplexing. To use the internal  $I^2C$  devices, the  $I^2C$  bus is permanently provided on the TQMa62xx. The following devices are connected to the module:

Figure 11: Block diagram I2C bus on the TQMa62xx

Table 9: I2C address assignment on the module

| Bus  | Component                  | Address           | Note            |

|------|----------------------------|-------------------|-----------------|

|      | Temperature sensor TMP1075 | 0x4A / 0b100 1010 |                 |

|      | EEPROM M24C02              | 0x50 / 0b101 0000 | TQ-Data         |

|      | EEPROM M24C64              | 0x54 / 0b101 0100 | Customer EEPROM |

| I2C0 | RTC PCF85063ATL            | 0x51 / 0b101 0001 |                 |

|      | SEC                        | 0x48 / 0b100 1000 |                 |

|      | PMIC TPS6521902            | 0x30 / 0b011 0000 |                 |

If additional devices should be connected to this bus, optional external pullups should be provided to improve the rise / fall times. I2C0 relates to 1.8V.

#### 3.2.8.4 UART

UART0 is routed to the TQMa62xxL pins as primary function.

#### 3.2.8.5 EXTINT#

The signal EXTINT# of the AM62x is routed to TQMa62xxL pin X2-B32 as primary function.

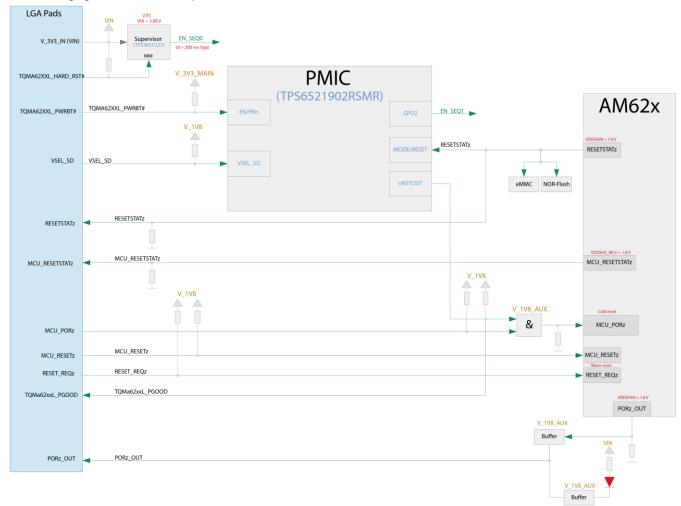

#### 3.2.9 Reset

The following figure describes the implementation of the reset structure of the TQMa62xxL:

Figure 12: Block diagram Reset

#### 3.2.9.1 Reset Options (Input)

## 3.2.9.1.1 TQMa62xxL\_HARD\_RST#

The input signal TQM62xxL\_HARD\_RST# is used to control the entire module. Coming from the module connectors a reset with power cycle of the module is executed. As soon as the signal becomes HIGH, the power-up sequencing takes place after a delay of approx. 200 ms.

Per default the signal is connected with a pullup to V\_3V3\_IN (3.3 V), therefore only a LOW can reset the module with power cycle.

## 3.2.9.1.2 TQMa62xxL\_PWRBT#

The input signal TQMa62xxL\_PWRBT# is used to control the entire module. Coming from the module connector an ON/OFF request at the PMIC is performed by the signal. An 8 s LOW level event leads to an OFF request of the PMIC. A 600 ms HIGH level event leads to an ON request of the PMIC.

It must be ensured that the "First Supply Detection" is activated on the PMIC. The TQMa62xxL\_PWRBT# signal is only ignored during the first power-up of the module.

Per default the signal is connected with a pullup to V\_3V3\_IN (3.3 V), therefore only a LOW can reset the module with power cycle.

#### 3.2.9.1.3 MCU\_PORz

The MCU\_PORz signal is used to control a cold reset. Between the module connector signal MCU\_PORz and the AM62x MCU\_PORz signal is an AND element and a PMIC, which keeps the signal at LOW during power sequencing and pulls it HIGH afterwards.

By default the signal is connected with a pullup to 1.8 V, so only a LOW can trigger a cold reset of the module.

# 3.2.9.1.4 MCU\_RESETz

The MCU\_RESETz signal is used to control a warm reset of the MCU domain of the AM62x.

By default the signal is connected to a pullup to 1.8 V, so only a LOW can trigger a warm reset of the MCU domain on the module.

#### 3.2.9.1.5 RESET\_REQz

The RESET\_REQz signal is used to control a warm reset of the main domain of the AM62x.

By default the signal is connected to a pullup to 1.8 V, so only a LOW can trigger a warm reset of the main domain on the module.

#### 3.2.9.2 Reset Status (Output)

#### 3.2.9.2.1 PORz\_OUT

The PORz\_OUT signal serves as status signal for a cold reset of the main domain of the AM62x.

By default the signal is driven via a buffer with 1.8 V.

#### 3.2.9.2.2 MCU\_RESETSTATz

The MCU\_RESETSTATz signal serves as a status signal for a warm reset of the MCU domain.

By default the signal is connected with a pulldown to ground.

#### 3.2.9.2.3 RESETSTATz

The RESETSTATz signal serves as a status signal for a warm reset of the main domain.

By default the signal is connected with a pulldown to ground.

### 3.2.9.3 Control signals

# 3.2.9.3.1 TQMa62xxL\_PGOOD

TQMa62xxL\_PGOOD serves as a status signal to the base board that the voltages on the main board can now be switched on. Power GOOD (PGOOD) is only active when the power sequencing on the module has been successfully completed.

#### 3.2.9.3.2 VSEL\_SD

VSEL\_SD is used to select the V\_VDDSHV5 supply voltage:

- LOW: V\_VDDSHV5 = 1.8 V

- HIGH: V\_VDDSHV5 = 3.3 V

By default the signal is connected with a pullup to 3.3 V, thus initially V\_VDDSHV5 is always supplied with 3.3 V.

#### 3.2.10 Watchdog

The AM62 provides a Watchdog Timer. If the Watchdog Timer is active and not reset within the specified time, triggers a Warm-Reset. For more information, refer to the AM62 Reference Manual (2).

# 3.2.11 Power supply

# 3.2.11.1 Main power supply

The main supply of the TQMa62xxL is defined to typ. 3.3 V. By applying the 3.3 V voltage the module generates all required voltages.

Figure 13: Block diagram power supply

# 3.2.11.2 Overview TQMa62xxL supply

The following table shows all relevant supply voltages of the TQMa62xxL.

Table 10: Supply voltages

| Module pin / Signal    | Voltage            | Current      | Use                                                                                                                                                          |

|------------------------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V_3V3_IN               | 3.201 V to 3.399 V | see Table 11 | Input: module supply                                                                                                                                         |

| V_3V3                  | 3.201 V to 3.399 V | max. 100 mA  | Output                                                                                                                                                       |

| V_1V8                  | 1.746 V to 1.854 V | max. 100 mA  | Output: for boot configuration                                                                                                                               |

| V_VDDSHV5              | 1.8 V / 3.3 V      | < 10 mA      | Output: MMC1 IO-Bank supply                                                                                                                                  |

| V_RTC_IN               | 2.0 V to 5.5 V     | See 3.2.5    | Input: supply for module RTC                                                                                                                                 |

| V_VPP                  | 1.8 V              | max. 400 mA  | Input: supply for eFuse programming                                                                                                                          |

| USB0_VBUS<br>USB1_VBUS | typ. 5 V           | < 1 mA       | Input: Used to detect the USB-VBUS voltage and is usually supplied with the VBUS voltage switched by the USB host. External circuitry is required – see (2). |

# Attention: Malfunction

If the absolute maximum voltages of the CPU are exceeded, malfunctions and component failures may occur. The mentioned outputs may not be supplied externally under any circumstances.

#### 3.2.11.3 Power sequenzing

After switching on the module supply V\_3V3\_IN and TQMa62xxL\_HARD\_RST# to HIGH the power-up sequence starts. With completion of the power sequencing the supply of the external mainboard components is signaled via TQM62xxL\_PGOOD. The following figure shows the chronological sequence of the signals involved.

Figure 14: Recommended power up sequence

## **Attention: Malfunction**

To avoid cross-supply and errors in the power-up sequence, no I/O pins may be driven by external components until the power-up sequence is completed. The end of the power-up sequence is signaled by a high level of the TQM62xxL\_PGOOD signal.

## 3.2.11.4 Power modes

The TQMa62xxL has the following power modes:

• Active Mode - The module is powered and everything is active.

Depending of the CPU, the following low power modes can be provided:

- Deep Sleep Mode

- o Module is completely powered

- All power domains except GP\_Core\_CTL and all clocks OFF

- o DDR interface in self-refresh

- MCU Only

- o Module is completely supplied

- All power domains except GP\_Core\_CTL and all clocks ON

- o DDR interface in self-refresh

- Standby

- o Module is completely supplied

- o All power domains and clocks ON

- o DDR interface in self-refresh

More information can be found in the AM62x Reference Manual (2).

Independent of the CPU, the following low power modes can be provided:

- Module RTC Mode

- o Module is no longer supplied via V\_3V3\_IN

- Only the V\_RTC\_IN remains supplied and active

- o The current consumption is then only determined by the current consumption of the RTC.

- Self-Refresh Mode (Suspend to RAM)

- o The LPDDR4 memory can be put into self-refresh mode by an SRE command.

- o IDD6 is specified in self-refresh, typ. current consumption at 25 °C ambient temperature is approx. 0.4 mA to 2.7 mA

#### 3.2.11.5 Power consumption

The following table lists some technical parameters of the module supply. The specified current consumptions are to be regarded as a guide value. Since the current consumption of the TQMa62xxL can differ greatly depending on the application, modes and operating system, the values listed here should only be used for a performance estimate.

Table 11: Current consumption TQMa62xxL

| TQMa62xxL                                                                                                                       |        |                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------|

| Current consumption Power OFF                                                                                                   | TBD mA | TQMa62xxL_HARD_RST# = LOW                                                                |

| Current consumption Reset mode                                                                                                  | TBD mA | MCU_PORz = LOW                                                                           |

| Current consumption Power Down                                                                                                  | TBD mA | TQMa62xxL_PWRBT# = LOW                                                                   |

| Current consumption theoretical worst case                                                                                      | 2.4 A  | Current consumption @ 3.3 V                                                              |

| Current consumption U-Boot prompt                                                                                               | TBD mA | U-Boot Idle                                                                              |

| Current consumption Linux prompt                                                                                                | TBD mA | Linux Idle                                                                               |

| Current consumption Linux<br>(stressapptest -W -s 31536000 -M 256 -m 4 -C 4 -i 4<br>stress-ngcpu-load 100cpu 4timeout 31536000) | TBD mA | Higher current consumption must be expected when using additional interfaces in parallel |

# 3.3 TQMa62xxL interface

#### 3.3.1 Pin assignment

The TQMa62xxL has a total of 366 LGA pads. By using the LGA design, the module is soldered on once and thus has a permanent, stable connection to its peripherals. Removing the module from its soldered-on position is not possible without further ado, is not recommended and can lead to a reduction in service life or to its destruction.

The electrical and pin characteristics are to be taken from the AM62x datasheet / manual (1)(2)

#### Attention: Destruction or malfunction

The multiple pin configurations of all AM62x internal function units must be taken note of. The pin assignment shown in Figure 15 refers to the corresponding BSP provided by TQ-Systems GmbH. Table 12 shows all pin multiplexing options.

Figure 15: Pad placement

# 3.3.2 Pinout TQMa62xxL

Table 12: Pinout

|            | : Pinout                       |             |          |                     |

|------------|--------------------------------|-------------|----------|---------------------|

| Module Pad | Signal                         | CPU BALL    | Ю        | Description / Usage |

|            | VOLTO BOLK                     | Main Domain |          |                     |

|            | VOUTO_PCLK                     |             | 0        | -                   |

|            | GPMC0_A19                      |             | OZ       | -                   |

|            | PRO_PRU1_GPO19                 |             | 0        | -                   |

| D22        | PRO_PRU1_GPI19                 | 1624        | <u> </u> | -                   |

| P22        | UART2_CTSn                     | AC24        | 10       | -                   |

|            | PRO_PRUO_GPO19                 |             | IO .     | -                   |

|            | PRO_PRUO_GPI19                 |             | I<br>10  | -                   |

|            | GPIO0_64 PR0_ECAP0_IN_APWM_OUT |             | 10       | -                   |

|            | VOUTO_HSYNC                    |             | 0        | -                   |

|            | GPMC0_A16                      |             | OZ       |                     |

|            | PRO_PRU1_GPO15                 |             | 0        | 1                   |

|            | PRO_PRU1_GPI15                 |             | I        | 1                   |

| N21        | UART3_RTSn                     | AB24        | 0        |                     |

|            | PRO_PRUO_GPO6                  |             | 10       | 1                   |

|            | PRO_PRUO_GPI6                  |             | I        |                     |

|            | GPIO0_61                       |             | IO       | 1                   |

|            | VOUTO_VSYNC                    |             | 0        | 1                   |

|            | GPMC0_A18                      |             | OZ       | 1                   |

|            | PRO_PRU1_GPO18                 |             | 0        | 1                   |

|            | PRO_PRU1_GPI18                 |             |          | -                   |

| N22        | UART2_RTSn                     | AC25        | 0        | -                   |

|            | PRO_PRUO_GPO18                 |             | 10       | -                   |

|            | PRO_PRUO_GPI18                 |             |          | 1                   |

|            | GPIO0_63                       |             | 10       | -                   |

|            | VOUTO_DE                       |             | 0        | 1                   |

|            | GPMC0_A17                      |             | OZ       |                     |

|            | PR0_PRU1_GPO17                 |             | 0        |                     |

|            | PRO_PRU1_GPI17                 |             | ı        | IO Muxing Options   |

| M21        | UART3_CTSn                     | Y20         | i        | To Maxing options   |

|            | PR0_PRU0_GPO7                  |             | IO       |                     |

|            | PRO_PRUO_GPI7                  |             | ı        |                     |

|            | GPIO0_62                       |             | 10       |                     |

|            | VOUTO_DATA0                    |             | 0        |                     |

|            | GPMC0_A0                       |             | OZ       |                     |

|            | PR0_PRU1_GPO0                  |             | 0        |                     |

| 1420       | PR0_PRU1_GPI0                  | 1122        | ı        |                     |

| M20        | UART2_RXD                      | U22         | ı        |                     |

|            | PR0_PRU0_GPO8                  |             | Ю        |                     |

|            | PRO_PRUO_GPI8                  |             | I        | ]                   |

|            | GPIO0_45                       |             | Ю        |                     |

|            | VOUT0_DATA1                    |             | 0        |                     |

|            | GPMC0_A1                       |             | OZ       |                     |

|            | PR0_PRU1_GPO1                  |             | 0        |                     |

| L20        | PR0_PRU1_GPI1                  | V24         | ı        |                     |

| LZU        | UART2_TXD                      | V 24        | 0        |                     |

|            | PR0_PRU0_GPO9                  |             | 10       |                     |

|            | PRO_PRUO_GPI9                  |             | ı        |                     |

|            | GPIO0_46                       |             | 10       |                     |

|            | VOUT0_DATA2                    |             | 0        |                     |

|            | GPMC0_A2                       |             | OZ       |                     |

|            | PR0_PRU1_GPO2                  |             | 0        |                     |

| L19        | PR0_PRU1_GPI2                  | W25         | Ι        |                     |

| LID        | UART3_RXD                      | VV23        | I        |                     |

|            | PR0_PRU0_GPO10                 |             | Ю        |                     |

|            | PRO_PRUO_GPI10                 |             | I        |                     |

|            | GPIO0_47                       |             | 10       |                     |

| Madula Pad | Cianal               | CDLLBALL | 10       | Description / Usage |

|------------|----------------------|----------|----------|---------------------|

| Module Pad | Signal VOUT0_DATA3   | CPU BALL | 10<br>0  | Description / Usage |

|            | GPMC0_A3             |          | OZ       | -                   |

|            | PR0_PRU1_GPO3        |          | 0        | -                   |

|            | PRO_PRU1_GPI3        |          |          | -                   |

| K19        | UART3_TXD            | W24      | 0        | -                   |

|            |                      |          |          | -                   |

|            | PRO_PRUO_GPO11       |          | IO<br>I  | -                   |

|            | PRO_PRUO_GPI11       |          | IO       | -                   |

|            | GPIO0_48 VOUT0_DATA4 |          | 0        | -                   |

|            |                      |          | OZ       | -                   |

|            | GPMC0_A4             |          |          | -                   |

|            | PRO_PRU1_GPO4        |          | 0        | -                   |

| K18        | PRO_PRU1_GPI4        | Y25      | <u> </u> | -                   |

|            | UART4_RXD            |          | 10       | -                   |

|            | PRO_PRUO_GPO12       |          | IO .     | -                   |

|            | PRO_PRUO_GPI12       |          | 10       | -                   |

|            | GPIO0_49             |          | 10       | -                   |

|            | VOUTO_DATA5          |          | 0        | 4                   |

|            | GPMC0_A5             |          | OZ       | -                   |

|            | PR0_PRU1_GPO5        |          | 0        | 1                   |

| J18        | PR0_PRU1_GPI5        | Y24      | I        | 1                   |

| 3.0        | UART4_TXD            |          | 0        | _                   |

|            | PR0_PRU0_GPO13       |          | 10       | _                   |

|            | PR0_PRU0_GPI13       |          | I        |                     |

|            | GPIO0_50             |          | 10       |                     |

|            | VOUT0_DATA6          |          | 0        |                     |

|            | GPMC0_A6             |          | OZ       |                     |

|            | PR0_PRU1_GPO6        |          | 0        |                     |

| U22        | PR0_PRU1_GPI6        | Y23      | I        | IO Muxing Options   |

| 022        | UART5_RXD            | 125      | I        |                     |

|            | PR0_PRU0_GPO14       |          | Ю        |                     |

|            | PR0_PRU0_GPI14       |          | I        |                     |

|            | GPIO0_51             |          | Ю        |                     |

|            | VOUT0_DATA7          |          | 0        |                     |

|            | GPMC0_A7             |          | OZ       |                     |

|            | PR0_PRU1_GPO7        |          | 0        |                     |

| T22        | PR0_PRU1_GPI7        | AA25     | -        |                     |

| 122        | UART5_TXD            | AAZS     | 0        |                     |

|            | PR0_PRU0_GPO15       |          | Ю        |                     |

|            | PR0_PRU0_GPI15       |          | I        |                     |

|            | GPIO0_52             |          | Ю        |                     |

|            | VOUT0_DATA8          |          | 0        |                     |

|            | GPMC0_A8             |          | OZ       |                     |

|            | PR0_PRU1_GPO16       |          | 0        | ]                   |

| T21        | PR0_PRU1_GPI16       | 1/21     | ı        | ]                   |

| T21        | UART6_RXD            | V21      | I        | 1                   |

|            | PR0_PRU0_GPO17       |          | Ю        | ]                   |

|            | PR0_PRU0_GPI17       |          | I        | 1                   |

|            | GPIO0_53             |          | Ю        | 1                   |

|            | VOUTO_DATA9          |          | 0        | 1                   |

|            | GPMC0_A9             |          | OZ       | 1                   |

|            | PR0_PRU1_GPO8        |          | 0        | 1                   |

| Do.        | PR0_PRU1_GPI8        |          |          | 1                   |

| R21        | UART6_TXD            | W21      | 0        | 1                   |

|            | PR0_PRU0_GPO16       |          | 10       | 1                   |

|            | PRO_PRUO_GPI16       |          | I        | 1                   |

|            | GPIO0_54             |          | IO       |                     |

|            |                      |          |          | 1                   |

| Module Pad | Signal                      | CPU BALL      | Ю        | Description / Usage |

|------------|-----------------------------|---------------|----------|---------------------|

| Wodale Fad | VOUT0_DATA10                | CI O DI ILL   | 0        | Description, Gaage  |

|            | GPMC0_A10                   |               | OZ       |                     |

|            | PR0_PRU1_GPO9               |               | 0        |                     |

|            | PRO_PRU1_GPI9               |               | ı        |                     |

| R20        | UART6_RTSn                  | V20           | 0        |                     |

|            | PR0_PRU0_GPO0               |               | Ю        |                     |

|            | PRO_PRUO_GPIO               |               | ı        |                     |

|            | GPIO0_55                    |               | IO       |                     |

|            | VOUTO_DATA11                |               | 0        |                     |

|            | GPMC0_A11                   |               | OZ       |                     |

|            | PR0_PRU1_GPO10              |               | 0        |                     |

|            | PRO_PRU1_GPI10              |               | Ī        |                     |

| P20        | UART6_CTSn                  | AA23          | i        |                     |

|            | PR0_PRU0_GPO1               |               | IO       |                     |

|            | PRO_PRUO_GPI1               |               | ı        |                     |

|            | GPIO0_56                    |               | IO       |                     |

|            | VOUTO_DATA12                |               | 0        |                     |

|            | GPMC0_A12                   |               | OZ       | 1                   |

|            | PRO_PRU1_GPO11              |               | 0        | 1                   |

|            | PRO_PRU1_GPI11              |               | Ī        | -                   |

| P19        | UART5_RTSn                  | AB25          | 0        | 1                   |

|            | PRO_PRUO_GPO2               |               | 10       | 1                   |

|            | PRO_PRUO_GPI2               |               | 10       | 1                   |

|            | GPIO0_57                    |               | IO       | 1                   |

|            | VOUT0_DATA13                |               | 0        | 1                   |

|            | GPMC0_A13                   |               | OZ       | 1                   |

|            | PRO_PRU1_GPO12              |               | 0        |                     |

|            | PRO_PRU1_GPI12              |               | I        |                     |

| N19        | UART5_CTSn                  | AA24          | <u> </u> | IO Muxing Options   |

|            | PRO_PRUO_GPO3               |               | 10       | 10 Muxing Options   |

|            | PRO_PRUO_GPI3               |               | I        |                     |

|            | GPIO0_58                    |               | IO       | 1                   |

|            | VOUT0_DATA14                |               | 0        |                     |

|            | GPMC0_A14                   |               | OZ       |                     |

|            | PRO_PRU1_GPO13              |               | 0        |                     |

|            | PRO_PRU1_GPI13              |               | ı        | -                   |

| N18        |                             | Y22           |          | -                   |

|            | UART4_RTSn                  |               | 0<br>10  | -                   |

|            | PRO_PRUO_GPO4               |               |          | -                   |

|            | PRO_PRUO_GPI4 GPIOO_59      | <del> </del>  | I<br>IO  | -                   |

|            | VOUTO_DATA15                |               | 0        | 1                   |

|            | GPMC0_A15                   | _             | OZ       | 1                   |

|            | PRO_PRU1_GPO14              | _             | 02       | 1                   |

|            | PRO_PRU1_GPU14              |               | I        | 1                   |

| M18        | UART4_CTSn                  | AA21          | <u> </u> | -                   |

|            |                             |               | 10       | 1                   |

|            | PR0_PRU0_GPO5 PR0_PRU0_GPI5 | <del> </del>  | IO<br>I  | -                   |

|            | GPIO0_60                    | $\overline{}$ | IO       | 1                   |

|            | _                           |               | 10       | 1                   |

|            | GPMC0_AD0                   | _             | 0        | 1                   |

|            | PRO_PRU1_GPO8               | $\overline{}$ | I        | 1                   |

|            | PRO_PRU1_GPI8               |               |          | -                   |

| C21        | MCASP2_AXR4                 | A435          | 10       | -                   |

| C21        | PRO_PRUO_GPOO               | M25           | 10       | -                   |

|            | PRO_PRUO_GPIO               | _             | 1        | -                   |

|            | TRC_CLK                     | <del> </del>  | 0        | -                   |

|            | GPIO0_15                    |               | IO       | -                   |

|            | BOOTMODE00                  |               | ı        |                     |

| Module Pad | Signal         | CPU BALL | IO      | Description / Usage |

|------------|----------------|----------|---------|---------------------|

|            | GPMC0_AD1      |          | IO      |                     |

|            | PR0_PRU1_GPO9  | 1        | 0       |                     |

|            | PR0_PRU1_GPI9  | 1        | I       |                     |

|            | MCASP2_AXR5    | 1        | Ю       |                     |

| D21        | PR0_PRU0_GPO1  | N23      | IO      |                     |

| 52.        | PRO_PRUO_GPI1  | 1.120    | ı       |                     |

|            | TRC_CTL        | 1        | 0       |                     |

|            | GPIO0_16       | 1        | 10      |                     |

|            | BOOTMODE01     | 1        | <u></u> |                     |

|            | GPMC0_AD2      |          | IO      |                     |

|            | PR0_PRU1_GPO10 | 1        | 0       |                     |

|            | PRO_PRU1_GPI10 | 1        | 1       |                     |

|            | MCASP2_AXR6    | 1        | IO      |                     |

| B20        | PRO_PRUO_GPO2  | N24      | 10      |                     |

| 520        | PRO_PRUO_GPI2  | 1121     | l I     |                     |

|            | TRC_DATA0      | 1        | 0       |                     |

|            | GPIO0_17       | -        | 10      |                     |

|            | BOOTMODE02     | -        | I       |                     |

|            | GPMC0_AD3      |          | IO      |                     |

|            | PR0_PRU1_GPO11 | -        | 0       |                     |

|            | PR0_PRU1_GPI11 | -        |         |                     |

|            | MCASP2_AXR7    | -        | IO      |                     |

| C20        | PRO_PRUO_GPO3  | N25      | 10      |                     |

| C20        | PRO_PRUO_GPI3  | 1123     | I       |                     |

|            | TRC_DATA1      |          | 0       |                     |

|            | GPIO0_18       | -        | 10      |                     |

|            | BOOTMODE03     | -        | I       |                     |

|            | GPMC0_AD4      |          | 10      | IO Muxing Options   |

|            | PR0_PRU1_GPO12 | -        | 0       |                     |

|            | PRO_PRU1_GPI12 | 1        |         |                     |

|            | MCASP2_AXR8    | 1        | IO      |                     |

| G22        | PRO_PRUO_GPO4  | P24      | IO      |                     |

| GZZ        | PRO_PRUO_GPI4  | F 24     |         |                     |

|            | TRC_DATA2      | 1        | 0       |                     |

|            | GPIO0_19       | 1        | IO      |                     |

|            | BOOTMODE04     | 1        | l I     |                     |

|            | GPMC0_AD5      |          | IO      |                     |

|            | PRO_PRU1_GPO13 | 1        | 0       |                     |

|            | PRO_PRU1_GPI13 |          | ı       |                     |

|            | MCASP2_AXR9    |          | IO      |                     |

| H22        | PR0_PRU0_GPO5  | P22      | 10      |                     |

|            | PRO_PRUO_GPI5  | 1        | ı       |                     |

|            | TRC_DATA3      |          | 0       |                     |