# TQMa93xxLA User's Manual

TQMa93xxLA UM 0007 11.03.2024

# TABLE OF CONTENTS

| 1.                   | ABOUT THIS MANUAL                                 | 1  |

|----------------------|---------------------------------------------------|----|

| 1.1                  | Copyright and license expenses                    | 1  |

| 1.2                  | Registered trademarks                             | 1  |

| 1.3                  | Disclaimer                                        | 1  |

| 1.4                  | Imprint                                           | 1  |

| 1.5                  | Tips on safety                                    | 2  |

| 1.6                  | Symbols and typographic conventions               |    |

| 1.7                  | Handling and ESD tips                             |    |

| 1.8                  | Naming of signals                                 |    |

| 1.9                  | Further applicable documents / presumed knowledge |    |

| 2.                   | BRIEF DESCRIPTION                                 |    |

| 2.1                  | Key functions and characteristics                 |    |

| 2.1                  | CPU block diagram                                 |    |

|                      | ELECTRONICS                                       |    |

| 3.                   |                                                   |    |

| 3.1                  | Interfaces to other systems and devices           |    |

| 3.1.1                | Pin multiplexing                                  |    |

| 3.1.1.1              | Pinout TQMa93xxLA                                 |    |

| 3.1.1.2              | TQMa93xxLA signals                                |    |

| 3.2                  | System components                                 |    |

| 3.2.1                | i.MX 93                                           |    |

| 3.2.1.1              | i.MX 93 derivatives                               |    |

| 3.2.1.2              | i.MX 93 errata                                    |    |

| 3.2.1.3              | Boot modes                                        |    |

| 3.2.1.4              | Boot configuration                                |    |

| 3.2.2                | Memory                                            | 13 |

| 3.2.2.1              | LPDDR4 SDRAM                                      | 13 |

| 3.2.2.2              | eMMC                                              | 13 |

| 3.2.2.3              | QSPI NOR Flash / NAND Flash                       |    |

| 3.2.2.4              | EEPROM M24C64-D                                   | 14 |

| 3.2.2.5              | EEPROM with temperature sensor SE97BTP            | 14 |

| 3.2.3                | Trust Secure Element SE050                        | 14 |

| 3.2.4                | Accelerometer/Gyroscope                           | 15 |

| 3.2.5                | RTC                                               | 15 |

| 3.2.5.1              | i.MX 93 internal RTC                              | 15 |

| 3.2.5.2              | Discrete RTC PCF85063A                            | 15 |

| 3.2.6                | Interfaces                                        | 16 |

| 3.2.6.1              | Overview                                          |    |

| 3.2.6.2              | ADC                                               |    |

| 3.2.6.3              | CAN FD                                            | 17 |

| 3.2.6.4              | Ethernet / RGMII                                  |    |

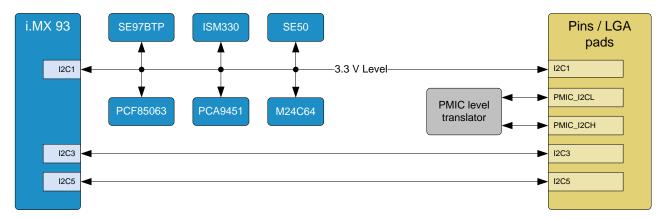

| 3.2.6.5              | I <sup>2</sup> C                                  |    |

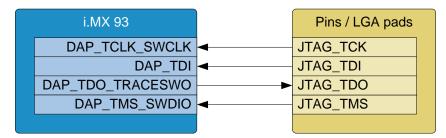

| 3.2.6.6              | JTAG                                              |    |

| 3.2.6.7              | GPIO                                              |    |

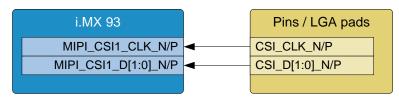

| 3.2.6.8              | MIPI CSI                                          |    |

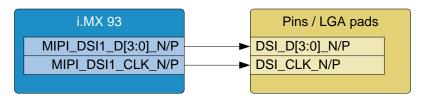

| 3.2.6.9              | MIPI DSI                                          |    |

| 3.2.6.10             | LVDS                                              |    |

| 3.2.6.11             | SAI                                               |    |

| 3.2.6.12             | SPI                                               |    |

| 3.2.6.13             | Tamper                                            |    |

| 3.2.6.14             |                                                   |    |

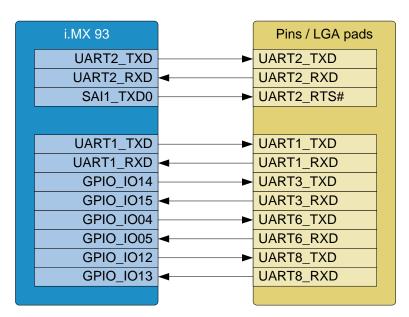

| 3.2.6.14<br>3.2.6.15 | UART                                              |    |

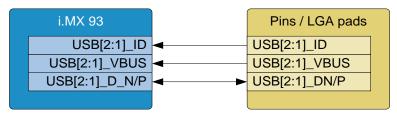

|                      | USB                                               |    |

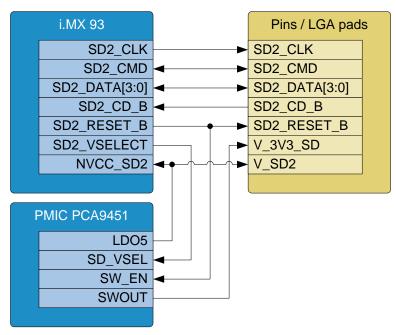

| 3.2.6.16             | SD2 (SD-Card)                                     |    |

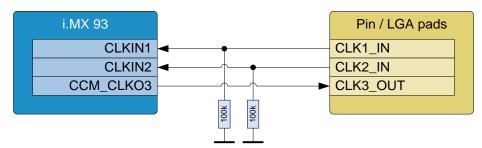

| 3.2.6.17             | External clock sources                            |    |

| 3.2.6.18             | TPM / PWM                                         |    |

| 3.2.7                | Reset and unspecific signals                      |    |

| 3.2.8                | Power                                             |    |

| 3.2.8.1              | Power supply                                      |    |

| 3.2.8.2              | Configurable voltages                             |    |

| 3.2.8.3              | Power consumption                                 |    |

| 3.2.8.4              | Voltage monitoring                                |    |

| 3.2.8.5              | Supply outputs                                    | 30 |

Page ii

# User's Manual | TQMa93xxLA UM 0007 | © 2024, TQ-Systems GmbH

| 3.2.8.6 | Power-Up sequence TQMa93xxLA / carrier board   | 30 |

|---------|------------------------------------------------|----|

| 3.2.8.7 | Standby and BBSM                               | 31 |

| 3.2.8.8 | PMIC                                           | 31 |

| 3.2.9   | Impedances                                     | 31 |

| 4.      | SOFTWARE                                       | 32 |

| 5.      | MECHANICS                                      | 33 |

| 5.1     | Dimensions                                     | 33 |

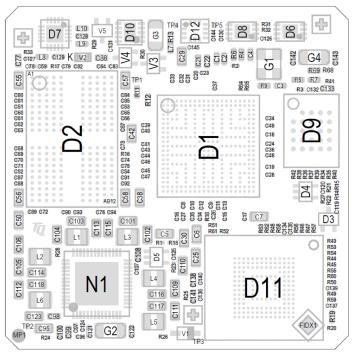

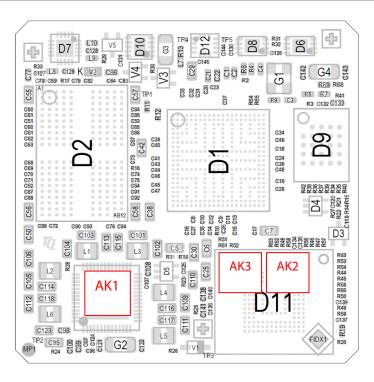

| 5.2     | Component placement and labeling               | 34 |

| 5.3     | Adaptation to the environment                  |    |

| 5.4     | Protection against external effects            | 36 |

| 5.5     | Thermal management                             | 36 |

| 5.6     | Structural requirements                        | 36 |

| 6.      | SAFETY REQUIREMENTS AND PROTECTIVE REGULATIONS | 37 |

| 6.1     | EMC                                            | 37 |

| 6.2     | ESD                                            | 37 |

| 6.3     | Shock and Vibration                            | 37 |

| 6.4     | Climate and operational conditions             | 38 |

| 6.5     | Operational safety and personal security       | 38 |

| 6.6     | Reliability and service life                   | 38 |

| 7.      | ENVIRONMENT PROTECTION                         | 39 |

| 7.1     | RoHS                                           | 39 |

| 7.2     | WEEE <sup>®</sup>                              |    |

| 7.3     | REACH <sup>®</sup>                             | 39 |

| 7.4     | EuP                                            | 39 |

| 7.5     | Battery                                        | 39 |

| 7.6     | Packaging                                      | 39 |

| 7.7     | Other entries                                  | 39 |

| 8.      | APPENDIX                                       | 40 |

| 8.1     | Acronyms and definitions                       | 40 |

| 8.2     | References                                     | 42 |

|         |                                                |    |

# TABLE DIRECTORY

| Table 1:  | Terms and conventions                          | 2  |

|-----------|------------------------------------------------|----|

| Table 2:  | Pinout TQMa93xxLA, top view through TQMa93xxLA | 6  |

| Table 3:  | TQMa93xxLA, signals                            | 7  |

| Table 4:  | i.MX 93 derivatives                            |    |

| Table 5:  | Boot configuration i.MX 93                     | 12 |

| Table 6:  | QSPI signals                                   | 13 |

| Table 7:  | ISO_7816 and ISO_14443 signals                 | 15 |

| Table 8:  | TQMa93xxLA interfaces                          | 16 |

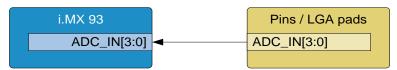

| Table 9:  | Pin assignment ADC                             | 17 |

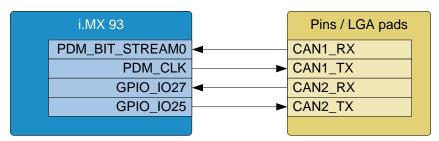

| Table 10: | CAN FD signals                                 | 17 |

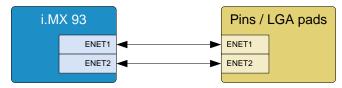

| Table 11: | ENET signals in RGMII mode                     | 18 |

| Table 12: | Address assignment I2C1 bus                    | 19 |

| Table 13: | Pin assignment I <sup>2</sup> C                | 19 |

| Table 14: | JTAG signals                                   | 20 |

| Table 15: | GPIO signals                                   | 20 |

| Table 16: | MIPI CSI signals                               | 21 |

| Table 17: | MIPI DSI signals                               | 21 |

| Table 18: | LVDS signals                                   | 22 |

| Table 19: | SAI signals                                    | 23 |

| Table 20: | Pinning SPI                                    | 23 |

| Table 21: | Pinning Tamper                                 | 24 |

| Table 22: | UART signals                                   | 25 |

| Table 23: | USB signals                                    | 25 |

| Table 24: | SD2 signals                                    | 26 |

| Table 25: | CLK signals                                    | 27 |

| Table 26: | TPM Signals                                    | 27 |

| Table 27: | Reset and unspecific signals                   | 28 |

| Table 28: | Power consumption                              | 29 |

| Table 29: | Voltages provided by TQMa93xxLA                | 30 |

| Table 30: | PMIC signals                                   | 31 |

| Table 31: | Trace impedance recommendations                | 31 |

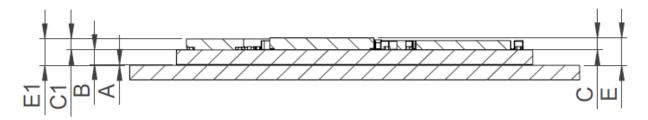

| Table 32: | TQMa93xxLA heights                             | 33 |

| Table 33: | Labels on TQMa93xxLA                           | 35 |

| Table 34: | Shock resistance                               | 37 |

| Table 35: | Vibration resistance                           | 37 |

| Table 36: | Climate and operational conditions             | 38 |

| Table 37: | Acronyms                                       | 40 |

| Table 38: | Further applicable documents                   | 42 |

# FIGURE DIRECTORY

| Figure 1:  | Block diagram i.MX 93                                   | 4  |

|------------|---------------------------------------------------------|----|

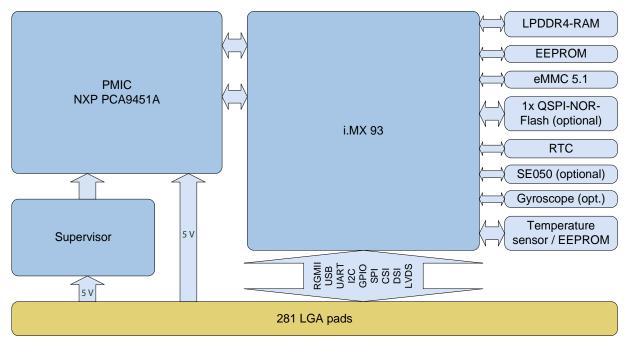

| Figure 2:  | Block diagram TQMa93xxLA (simplified)                   | 5  |

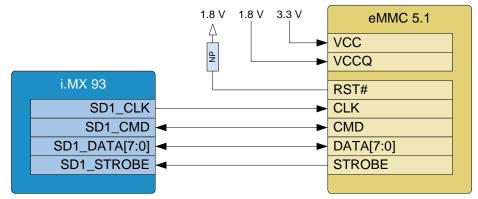

| Figure 3:  | Block diagram eMMC                                      | 13 |

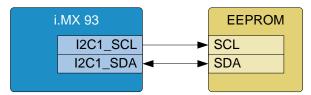

| Figure 4:  | Block diagram EEPROM                                    | 14 |

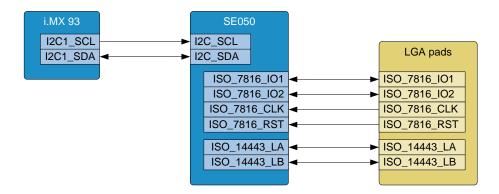

| Figure 5:  | Block diagram SE050                                     |    |

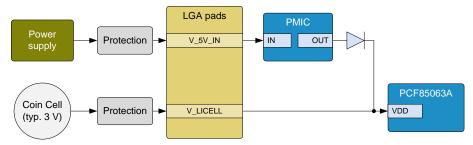

| Figure 6:  | Block diagram RTC supply (TQMa93xxLA with discrete RTC) | 16 |

| Figure 7:  | Block diagram ADC                                       | 17 |

| Figure 8:  | Block diagram CAN                                       | 17 |

| Figure 9:  | Block diagram RGMII                                     | 18 |

| Figure 10: | Block diagram I <sup>2</sup> C                          | 19 |

| Figure 11: | Block diagram JTAG interface                            | 20 |

| Figure 12: | Block diagram MIPI CSI                                  | 21 |

| Figure 13: | Block diagram MIPI DSI                                  | 21 |

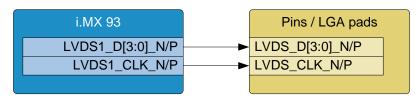

| Figure 14: | Block diagram LVDS                                      | 22 |

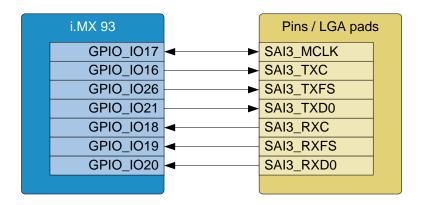

| Figure 15: | Block diagram SAI3                                      | 22 |

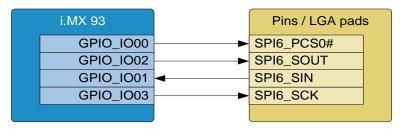

| Figure 16: | Block diagram SPI                                       | 23 |

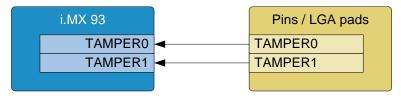

| Figure 17: | Block diagram Tamper                                    | 24 |

| Figure 18: | Block diagram UART interfaces                           | 24 |

| Figure 19: | Block diagram USB interfaces                            | 25 |

| Figure 20: | Block diagram SD card interface                         | 26 |

| Figure 21: | Block diagram external clocks                           | 27 |

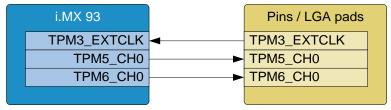

| Figure 22: | Block diagram TPM                                       | 27 |

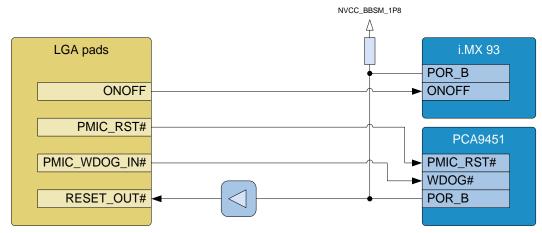

| Figure 23: | Block diagram Reset                                     | 28 |

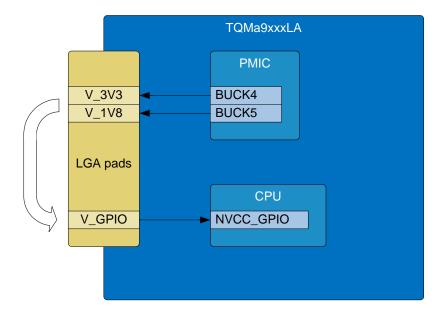

| Figure 24: | Possible power supply of the CPU-rail NVCC_GPIO         | 29 |

| Figure 25: | Block diagram power supply carrier board                | 30 |

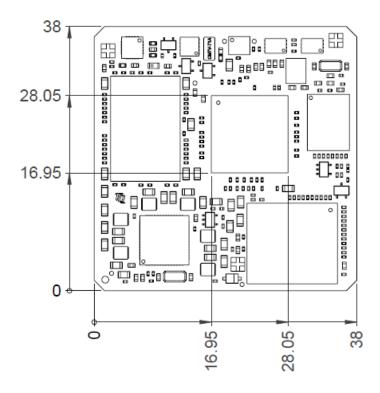

| Figure 26: | TQMa93xxLA dimensions, top view                         | 33 |

| Figure 27: | TQMa93xxLA dimensions, side view                        | 33 |

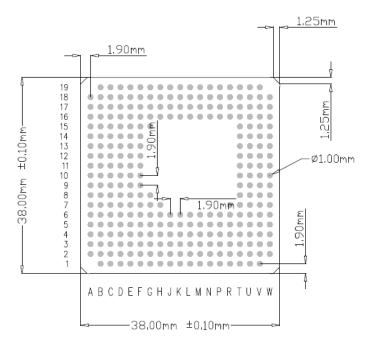

| Figure 28: | TQMa93xxLA dimensions, top through view                 | 34 |

| Figure 29: | TQMa93xxLA, component placement top                     | 34 |

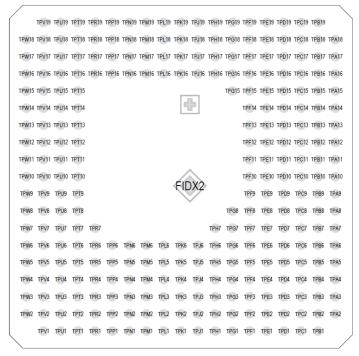

| Figure 30: | TQMa93xxLA, LGA pad numbering scheme, bottom view       |    |

| Figure 31: | Labels on TQMa93xxLA                                    | 35 |

# **REVISION HISTORY**

| Rev. | Date       | Name    | Pos.                                                                                                                                      | Modification                                                                 |

|------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 0001 | 1.12.2022  | Kreuzer |                                                                                                                                           | First issue                                                                  |

| 0002 | 27.2.2022  | Kreuzer | all                                                                                                                                       | Adjustments after internal review                                            |

| 0003 | 1.3.2023   | Kreuzer | all                                                                                                                                       | Typo, formating                                                              |

| 0004 | 16.3.2023  | Kreuzer | all                                                                                                                                       | Typo, formating                                                              |

| 0005 | 13.4.2023  | Kreuzer | all                                                                                                                                       | Stylistic revision                                                           |

| 0006 | 28.7.2023  | Kreuzer | Table 2, Table 3, 3.2.6.12, Figure 16, Table 20, 3.2.6.14, Figure 18, Table 22, 3.2.6.17, Figure 21, Table 25 3.2.18, Figure 22, Table 26 | Signal renaming for MBa93xxLA revision<br>0200 multiplexing<br>Chapter added |

| 0007 | 11.03.2024 | Kreuzer | Table 14                                                                                                                                  | Corrected                                                                    |

#### ABOUT THIS MANUAL

# 1.1 Copyright and license expenses

Copyright protected © 2024 by TQ-Systems GmbH.

This User's Manual may not be copied, reproduced, translated, changed or distributed, completely or partially in electronic, machine readable, or in any other form without the written consent of TQ-Systems GmbH.

The drivers and utilities for the components used as well as the BIOS are subject to the copyrights of the respective manufacturers. The licence conditions of the respective manufacturer are to be adhered to.

Bootloader-licence expenses are paid by TQ-Systems GmbH and are included in the price.

Licence expenses for the operating system and applications are not taken into consideration and must be calculated / declared separately.

#### 1.2 Registered trademarks

TQ-Systems GmbH aims to adhere to copyrights of all graphics and texts used in all publications, and strives to use original or license-free graphics and texts.

All brand names and trademarks mentioned in this User's Manual, including those protected by a third party, unless specified otherwise in writing, are subjected to the specifications of the current copyright laws and the proprietary laws of the present registered proprietor without any limitation. One should conclude that brand and trademarks are rightly protected by a third party.

#### 1.3 Disclaimer

TQ-Systems GmbH does not guarantee that the information in this User's Manual is up-to-date, correct, complete or of good quality. Nor does TQ-Systems GmbH assume guarantee for further usage of the information. Liability claims against TQ-Systems GmbH, referring to material or non-material related damages caused, due to usage or non-usage of the information given in this User's Manual, or due to usage of erroneous or incomplete information, are exempted, as long as there is no proven intentional or negligent fault of TQ-Systems GmbH.

TQ-Systems GmbH explicitly reserves the rights to change or add to the contents of this User's Manual or parts of it without special notification.

# **Important Notice:**

Before using the Starterkit MBa93xxLA or parts of the schematics of the MBa93xxLA, you must evaluate it and determine if it is suitable for your intended application. You assume all risks and liability associated with such use. TQ-Systems GmbH makes no other warranties including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. Except where prohibited by law, TQ-Systems GmbH will not be liable for any indirect, special, incidental or consequential loss or damage arising from the usage of the Starterkit MBa93xxLA or schematics used, regardless of the legal theory asserted.

## 1.4 Imprint

TQ-Systems GmbH Gut Delling, Mühlstraße 2

#### D-82229 Seefeld

Tel: +49 8153 9308-0 Fax: +49 8153 9308-4223 E-Mail: Info@TQ-Group Web: TQ-Group

# 1.5 Tips on safety

Improper or incorrect handling of the product can substantially reduce its life span.

# 1.6 Symbols and typographic conventions

Table 1: Terms and conventions

| Symbol    | Meaning                                                                                                                                                                                                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | This symbol represents the handling of electrostatic-sensitive modules and / or components. These components are often damaged / destroyed by the transmission of a voltage higher than about 50 V. A human body usually only experiences electrostatic discharges above approximately 3,000 V. |

| 4         | This symbol indicates the possible use of voltages higher than 24 V. Please note the relevant statutory regulations in this regard. Non-compliance with these regulations can lead to serious damage to your health and may damage or destroy the component.                                    |

| <u>^!</u> | This symbol indicates a possible source of danger. Ignoring the instructions described can cause health damage, or damage the hardware.                                                                                                                                                         |

| Â         | This symbol represents important details or aspects for working with TQ-products.                                                                                                                                                                                                               |

| Command   | A font with fixed-width is used to denote commands, contents, file names, or menu items.                                                                                                                                                                                                        |

# 1.7 Handling and ESD tips

# General handling of your TQ-products

The TQ-product may only be used and serviced by certified personnel who have taken note of the information, the safety regulations in this document and all related rules and regulations.

A general rule is not to touch the TQ-product during operation. This is especially important when switching on, changing jumper settings or connecting other devices without ensuring beforehand that the power supply of the system has been switched off.

Violation of this guideline may result in damage / destruction of the TQMa93xxLA and be dangerous to your health.

Improper handling of your TQ-product would render the guarantee invalid.

## **Proper ESD handling**

The electronic components of your TQ-product are sensitive to electrostatic discharge (ESD). Always wear antistatic clothing, use ESD-safe tools, packing materials etc., and operate your TQ-product in an ESD-safe environment. Especially when you switch modules on, change jumper settings, or connect other devices.

## 1.8 Naming of signals

A hash mark (#) at the end of the signal name indicates a low-active signal.

Example: RESET#

If a signal can switch between two functions and if this is noted in the name of the signal, the low-active function is marked with a hash mark and shown at the end.

Example: C / D#

If a signal has multiple functions, the individual functions are separated by slashes when they are important for the wiring. The identification of the individual functions follows the above conventions.

Example: WE2# / OE#

# 1.9 Further applicable documents / presumed knowledge

#### • Specifications and manual of the modules used:

These documents describe the service, functionality and special characteristics of the module used (incl. BIOS).

# • Specifications of the components used:

The manufacturer's specifications of the components used, for example CompactFlash cards, are to be taken note of. They contain, if applicable, additional information that must be taken note of for safe and reliable operation. These documents are stored at TQ-Systems GmbH.

#### • Chip errata:

It is the user's responsibility to make sure all errata published by the manufacturer of each component are taken note of. The manufacturer's advice should be followed.

#### • Software behaviour:

No warranty can be given, nor responsibility taken for any unexpected software behaviour due to deficient components.

# • General expertise:

Expertise in electrical engineering / computer engineering is required for the installation and the use of the device.

The following documents are required to fully comprehend the following contents:

- MBa93xxLA circuit diagram

- MBa93xxLA User's Manual

- i.MX 93 Data Sheet

- i.MX 93 Reference Manual

• U-Boot documentation: <u>www.denx.de/wiki/U-Boot/Documentation</u>

• PTXdist documentation: <u>www.ptxdist.de</u>

• Yocto documentation: <u>www.yoctoproject.org/docs/</u>

• TQ-Support Wiki: <u>Support-Wiki TQMa93xxLA (in progress)</u>

#### 2. BRIEF DESCRIPTION

This User's Manual describes the hardware of the TQMa93xxLA as of revision 0100, in combination with the MBa93xxLA as of revision 0200 and refers to some software settings. A certain TQMa93xxLA derivative does not necessarily provide all features described in this User's Manual.

This User's Manual does neither replace the i.MX 93 Reference Manual (1), nor the i.MX 93 Data Sheet (2), nor any other documents from NXP.

The TQMa93xxLA is a universal Minimodule based on the NXP ARM® Cortex®-A55 based i.MX 93 CPU family, see also Table 4.

# 2.1 Key functions and characteristics

The TQMa93xxLA extends the TQ-Systems GmbH product range and offers an outstanding computing performance.

All essential i.MX 93 signals are routed to the TQMa93xxLA LGA pads. There are therefore no restrictions for customers using the TQMa93xxLA with respect to an integrated customised design. All essential components like CPU, LPDDR4, eMMC, and PMIC are already integrated on the TQMa93xxLA.

The main features of the TQMa93xxLA are:

- 64 bit NXP i.MX 93 CPU, up to 2 × ARM Cortex<sup>®</sup>-A55 and 1 × Cortex<sup>®</sup>-M33

- Up to 2 Gbyte of LPDDR4- or LPDDR4X RAM

- Up to 256 Gbyte of eMMC NAND Flash, eMMC standard 5.1

- Up to 256 Mbyte QSPI NOR Flash (optional)

- 64 Kbit EEPROM (optional)

- Temperature sensor + EEPROM

- NXP Power Management Integrated Circuit PCA9451

- RTC (optional)

- Trust Secure Element (optional)

- Gyroscope (optional)

- All essential i.MX 93 signals are routed to the TQMa93xxLA LGA pads

- Single supply voltage 5 V

# 2.2 CPU block diagram

Figure 1: Block diagram i.MX 93

(Source: NXP)

#### 3. ELECTRONICS

The information provided in this User's Manual is only valid in connection with the tailored boot loader, which is preinstalled on the TQMa93xxLA, and the <u>BSP provided by</u> TQ-Systems GmbH, see also chapter 4.

Figure 2: Block diagram TQMa93xxLA (simplified)

# 3.1 Interfaces to other systems and devices

# 3.1.1 Pin multiplexing

The multiple pin configurations by different i.MX 93 internal function units must be taken note of.

The pin assignment in Table 3 refers to a TQMa93xxLAA with i.MX 93 CPU in combination with the carrier board MBa93xxLA.

NXP provides a tool showing the multiplexing and simplifies the selection and configuration (i.MX Pins Tool – NXP Tool).

The electrical and pin characteristics are to be taken from the i.MX 93 and PMIC documentation, see Table 40.

# Attention: Destruction or malfunction, pin multiplexing

Depending on the configuration, many i.MX 93 pins can provide several different functions. Please take note of the information concerning the configuration of these pins in the i.MX 93 Reference Manual (1), before integration or start-up of your carrier board / Starterkit. Improper programming by operating software can cause malfunctions, deterioration or destruction of the TQMa93xxLA.

The descriptions given in the following tables should be taken note of:

– DNC: These pins must never be connected and have to be left open.

Please contact **TQ-Support** for details.

# 3.1.1.1 Pinout TQMa93xxLA

The TQMa93xxLA has a total of 281 LGA pads. The TQMa93xxLA is soldered and thus permanently connected to the carrier board. It is not trivial and it is not recommended to remove the TQMa93xxLA.

The following table shows the TQMa93xxLA pad-out, top view through the TQMa93xxLA.

Table 2: Pinout TQMa93xxLA, top view through TQMa93xxLA

|    | Α                    | В                    | С                    | D                    | Е              | F               | G             | Н                     | J                | K             | L             | M                | N              | Р             | R              | Т              | U              | ٧               | W              |    |

|----|----------------------|----------------------|----------------------|----------------------|----------------|-----------------|---------------|-----------------------|------------------|---------------|---------------|------------------|----------------|---------------|----------------|----------------|----------------|-----------------|----------------|----|

| 19 |                      | Ground               | LVDS_<br>CLK_P       | LVDS_<br>CLK_N       | Ground         | LVDS_<br>D0_P   | LVDS_<br>D0_N | Ground                | DSI_CLK<br>_N    | DSI_CLK<br>_P | Ground        | CSI_D0_<br>N     | CSI_D0_<br>P   | CSI_D1_<br>N  | CSI_D1_<br>P   | Ground         | USB1_D<br>P    | USB1_D<br>N     |                | 19 |

| 18 | LVDS_<br>D3_P        | LVDS_<br>D3_N        | Ground               | LVDS_<br>D2_P        | LVDS_<br>D2_N  | Ground          | DSI_D0_<br>N  | DSI_D0_<br>P          | Ground           | DSI_D2_<br>N  | DSI_D2_<br>P  | Ground           | CSI_CLK<br>_N  | CSI_CLK<br>_P | DNC            | DNC            | Ground         | USB2_D<br>P     | USB2_D<br>N    | 18 |

| 17 | ISO_<br>7816_IO<br>1 | Ground               | ISO_<br>14443_L<br>B | Ground               | LVDS_<br>D1_P  | LVDS_<br>D1_N   | Ground        | DSI_D1_<br>N          | DSI_D1_<br>P     | Ground        | DSI_D3_<br>N  | DSI_D3_<br>P     | Ground         | USB1_<br>VBUS | Ground         | DNC            | DNC            | Ground          | ADC_IN0        | 17 |

| 16 | Ground               | ISO_<br>14443_L<br>A | Ground               | ISO_<br>7816_RS<br>T | M33_NM<br>I    | Ground          | CAN1_R<br>X   | CAN1_T<br>X           | Ground           | Tamper1       | Tamper0       | Ground           | USB1_ID        | USB2_ID       | Ground         | USB2_<br>VBUS  | Ground         | ADC_IN2         | ADC_IN1        | 16 |

| 15 | ISO_<br>7816_CL<br>K | ISO_<br>7816_IO<br>2 | Ground               | V_LICELL             | Ground         | TEMP_<br>EVENT# | Ground        |                       |                  |               |               |                  |                |               |                | GPIO1_<br>IO02 | CLK1_IN        | Ground          | ADC_IN3        | 15 |

| 14 | Ground               | ENET2_<br>MDIO       | RFU                  | Ground               | RTC_<br>EVENT# | Ground          |               | -                     |                  |               |               |                  |                |               |                | CLK2_IN        | Ground         | QSPI_<br>SCLK   | Ground         | 14 |

| 13 | ENET2_<br>MDC        | ENET2_R<br>D0        | RFU                  | RFU                  | Ground         | RFU             |               |                       |                  |               |               |                  |                |               |                | Ground         | QSPI_<br>SS0#  | QSPI_<br>DATA0  | QSPI_<br>DATA2 | 13 |

| 12 | ENET2_R<br>D2        | ENET2_R<br>D1        | RFU                  | Ground               | UART2_<br>RXD  | RFU             |               |                       |                  |               |               |                  |                |               |                | RFU            | QSPI_<br>DATA1 | Ground          | QSPI_<br>DATA3 | 12 |

| 11 | Ground               | ENET2_R<br>D3        | Ground               | UART1_<br>TXD        | UART2_<br>TXD  | Ground          |               |                       |                  |               |               |                  |                |               |                | V_SD2          | Ground         | GPIO1_<br>IO12  | Ground         | 11 |

| 10 | ENET2_<br>RXC        | Ground               | I2C1_SC<br>L         | UART1_<br>RXD        | Ground         | JTAG_TC<br>K    |               |                       |                  |               |               |                  |                |               |                | Ground         | GPIO1_<br>IO11 | GPIO1_<br>IO14  | UART2_<br>RTS# | 10 |

| 9  | ENET2_T<br>D0        | ENET2_<br>RX_CTL     | I2C1_SD<br>A         | Ground               | JTAG_TD<br>I   | JTAG_T<br>MS    |               | -                     |                  |               |               |                  |                |               |                | UART6_<br>TXD  | SPI6_<br>PCS0# | Ground          | V_GPIO         | 9  |

| 8  | Ground               | ENET2_T<br>D1        | Ground               | RFU                  | Ground         | JTAG_TD<br>O    | Ground        |                       | •                |               |               |                  |                |               |                | UART6_<br>RXD  | SPI6_<br>SIN   | SPI6_<br>SOUT   | SPI6_<br>SCK   | 8  |

| 7  | ENET2_T<br>D3        | Ground               | ENET2_T<br>D2        | Ground               | RFU            | Ground          | ONOFF         | Ground                |                  |               |               |                  |                |               | Ground         | TPM5_C<br>H0   | Ground         | Ground          | Ground         | 7  |

| 6  | ENET2_T<br>XC        | ENET2_<br>TX_CTL     | Ground               | Ground               | PMIC_RS<br>T#  | V_3V3_S<br>D    | Ground        | PMIC_<br>WDOG_I<br>N# | Ground           | WDOG_<br>ANY  | Ground        | RFU              | RFU            | Ground        | GPIO2_<br>IO07 | Ground         | TPM6_C<br>H0   | TPM3_<br>EXTCLK | GPIO2_<br>IO10 | 6  |

| 5  | Ground               | Ground               | Ground               | Ground               | Ground         | Ground          | PMIC_<br>SCLH | PMIC_<br>SCLL         | RESET_<br>OUT#   | Ground        | CAN2_R<br>X   | CAN2_T<br>X      | GPIO2_<br>IO24 | I2C5_SD<br>A  | Ground         | UART8_<br>TXD  | UART8_<br>RXD  | Ground          | GPIO2_<br>IO11 | 5  |

| 4  | V_5V_IN              | V_5V_IN              | V_5V_IN              | Ground               | Ground         | Ground          | PMIC_<br>SDAH | PMIC_<br>SDAL         | Ground           | I2C3_SC<br>L  | I2C3_SD<br>A  | Ground           | SAI3_TX<br>FS  | I2C5_SC<br>L  | UART3_<br>TXD  | UART3_<br>RXD  | Ground         | SD2_<br>DATA0   | Ground         | 4  |

| 3  | V_5V_IN              | V_5V_IN              | V_5V_IN              | Ground               | Ground         | Ground          | Ground        | ENET1_R<br>D2         | ENET1_<br>RX_CTL | Ground        | ENET1_T<br>D2 | ENET1_<br>TX_CTL | Ground         | SAI3_RX<br>FS | SAI3_TX<br>D0  | Ground         | SD2_<br>DATA2  | SD2_<br>DATA1   | SD2_CM<br>D    | 3  |

| 2  | V_5V_IN              | Ground               | Ground               | GPIO4_<br>IO29       | Ground         | ENET1_<br>MDIO  | ENET1_R<br>D0 | Ground                | ENET1_<br>RXC    | ENET1_T<br>D0 | Ground        | ENET1_T<br>XC    | SAI3_RX<br>D0  | Ground        | SAI3_RX<br>C   | SAI3_TX<br>C   | SD2_CD<br>#    | Ground          | SD2_CLK        | 2  |

| 1  |                      | GPIO3_<br>IO26       | GPIO3_<br>IO27       | CLK3_O<br>UT         | Ground         | ENET1_<br>MDC   | ENET1_R<br>D1 | ENET1_R<br>D3         | Ground           | ENET1_T<br>D1 | ENET1_T<br>D3 | Ground           | V_1V8          | V_3V3         | Ground         | SAI3_MC<br>LK  | SD2_RST<br>#   | SD2_<br>DATA3   |                | 1  |

|    | Α                    | В                    | С                    | D                    | Е              | F               | G             | Н                     | J                | K             | L             | М                | N              | Р             | R              | Т              | U              | ٧               | W              |    |

# 3.1.1.2 TQMa93xxLA signals

Details about the electrical characteristics of single pins and interfaces are to be taken from the i.MX 93 documentation (1), (2), (3), as well as the PMIC Data Sheet (4).

Table 3: TQMa93xxLA, signals

| TQMa93xxLAA | Ball name        | TQ multiplexing | Group | Dir. | Level | CPU<br>ball | Comment |

|-------------|------------------|-----------------|-------|------|-------|-------------|---------|

| pad<br>W17  | ADC_IN0          | ADC_IN0         | ADC   |      | 1,8 V | B19         |         |

| W17         | ADC_IN1          | ADC_IN1         | ADC   | H    | 1,8 V | A20         |         |

| V16         | ADC_IN1          | ADC_IN1         | ADC   | i    | 1,8 V | B20         |         |

| W15         | ADC_IN3          | ADC_IN3         | ADC   | i    | 1,8 V | B21         |         |

| B1          | CCM_CLKO1        | GPIO3_IO26      | GPIO  | 1/0  | 1,8 V | AA2         |         |

| C1          | CCM_CLKO2        | GPIO3_IO27      | GPIO  | 1/0  | 1,8 V | Y3          |         |

| D1          | CCM_CLKO3        | CLK3_OUT        | CLK   | 0    | 1,8 V | U4          |         |

| D2          | CCM_CLKO4        | GPIO4_IO29      | GPIO  | 1/0  | 1,8 V | V4          |         |

| U15         | CLKIN1           | CLK1_IN         | CLK   | 1    | 1,8 V | B17         |         |

| T14         | CLKIN2           | CLK2_IN         | CLK   | İ    | 1,8 V | A18         |         |

| F10         | DAP_TCLK_SWCLK   | JTAG_TCK        | JTAG  | 0    | 1,8 V | Y1          |         |

| E9          | DAP_TDI          | JTAG_TDI        | JTAG  | ī    | 1,8 V | W1          |         |

| F8          | DAP_TDO_TRACESWO | JTAG_TDO        | JTAG  | 0    | 1,8 V | Y2          |         |

| F9          | DAP_TMS_SWDIO    | JTAG TMS        | JTAG  | Ī    | 1,8 V | W2          |         |

| F1          | ENET1_MDC        | ENET_MDC        | ENET  | 0    | 1,8 V | AA11        |         |

| F2          | ENET1_MDIO       | ENET_MDIO       | ENET  | 1/0  | 1,8 V | AA10        |         |

| G2          | ENET1_RD0        | ENET_RD0        | ENET  | I    | 1,8 V | AA8         |         |

| G1          | ENET1_RD1        | ENET_RD1        | ENET  |      | 1,8 V | Y9          |         |

| H3          | ENET1_RD2        | ENET_RD2        | ENET  | ı    | 1,8 V | AA9         |         |

| H1          | ENET1_RD3        | ENET_RD3        | ENET  | 1    | 1,8 V | Y10         |         |

| J3          | ENET1_RX_CTL     | ENET_RX_CTL     | ENET  | ı    | 1,8 V | Y8          |         |

| J2          | ENET1_RXC        | ENET_RXC        | ENET  | I    | 1,8 V | AA7         |         |

| K2          | ENET1_TD0        | ENET_TD0        | ENET  | 0    | 1,8 V | W11         |         |

| K1          | ENET1_TD1        | ENET_TD1        | ENET  | 0    | 1,8 V | T12         |         |

| L3          | ENET1_TD2        | ENET_TD2        | ENET  | 0    | 1,8 V | U12         |         |

| L1          | ENET1_TD3        | ENET_TD3        | ENET  | 0    | 1,8 V | V12         |         |

| M3          | ENET1_TX_CTL     | ENET_TX_CTL     | ENET  | 0    | 1,8 V | V10         |         |

| M2          | ENET1_TXC        | ENET_TXC        | ENET  | 0    | 1,8 V | U10         |         |

| A13         | ENET2_MDC        | ENET2_MDC       | ENET  | 0    | 1,8 V | Y7          |         |

| B14         | ENET2_MDIO       | ENET2_MDIO      | ENET  | I/O  | 1,8 V | AA6         |         |

| B13         | ENET2_RD0        | ENET2_RD0       | ENET  | I    | 1,8 V | AA4         |         |

| B12         | ENET2_RD1        | ENET2_RD1       | ENET  | - 1  | 1,8 V | Y5          |         |

| A12         | ENET2_RD2        | ENET2_RD2       | ENET  | I    | 1,8 V | AA5         |         |

| B11         | ENET2_RD3        | ENET2_RD3       | ENET  | I    | 1,8 V | Y6          |         |

| B9          | ENET2_RX_CTL     | ENET2_RX_CTL    | ENET  | I    | 1,8 V | Y4          |         |

| A10         | ENET2_RXC        | ENET2_RXC       | ENET  | I    | 1,8 V | AA3         |         |

| A9          | ENET2_TD0        | ENET2_TD0       | ENET  | 0    | 1,8 V | T8          |         |

| B8          | ENET2_TD1        | ENET2_TD1       | ENET  | 0    | 1,8 V | U8          |         |

| C7          | ENET2_TD2        | ENET2_TD2       | ENET  | 0    | 1,8 V | V8          |         |

| A7          | ENET2_TD3        | ENET2_TD3       | ENET  | 0    | 1,8 V | T10         |         |

| B6          | ENET2_TX_CTL     | ENET2_TX_CTL    | ENET  | 0    | 1,8 V | V6          |         |

| A6          | ENET2_TXC        | ENET2_TXC       | ENET  | 0    | 1,8 V | U6          |         |

Table 3: TQMa93xxLA, signals (continued)

| Table 3:           | TQMa93xxLA, sign | ais (continued) |           |          |        |             |                                              |

|--------------------|------------------|-----------------|-----------|----------|--------|-------------|----------------------------------------------|

| TQMa93xxLAA<br>pad | Ball name        | TQ multiplexing | Group     | Dir.     | Level  | CPU<br>ball | Comment                                      |

| U9                 | GPIO_IO00        | SPI6_PCS0#      | SPI       | 0        | V_GPIO | J21         |                                              |

| U8                 | GPIO_IO01        | SPI6_SIN        | SPI       |          | V_GPIO | J20         |                                              |

| V8                 | GPIO_IO02        | SPI6_SOUT       | SPI       | 0        | V_GPIO | K20         |                                              |

| W8                 | GPIO_IO03        | SPI6_SCK        | SPI       | 0        | V_GPIO | K21         |                                              |

| T9                 | GPIO_IO04        | UART6_TXD       | UART      | 0        | V_GPIO | L17         |                                              |

| T8                 | GPIO_IO05        | UART6_RXD       | UART      | Ť        | V_GPIO | L18         |                                              |

| T7                 | GPIO_IO06        | TPM5_CH0        | TPM       | 0        | V_GPIO | L20         |                                              |

| R6                 | GPIO_IO07        | GPIO2_IO07      | GPIO      | 1/0      | V_GPIO | L21         |                                              |

| U6                 | GPIO_IO08        | TPM6_CH0        | TPM       | 0        | V_GPIO | M20         |                                              |

| V6                 | GPIO_IO09        | TPM3_EXTCLK     | TPM       | ī        | V_GPIO | M21         |                                              |

| W6                 | GPIO_IO10        | GPIO2_IO10      | GPIO      | I/O      | V_GPIO | N17         |                                              |

| W5                 | GPIO_IO11        | GPIO2_IO11      | GPIO      | 1/0      | V_GPIO | N18         |                                              |

| T5                 | GPIO_IO12        | UART8_TXD       | UART      | 0        | V_GPIO | N20         |                                              |

| U5                 | GPIO_IO13        | UART8_RXD       | UART      | 1        | V_GPIO | N21         |                                              |

| R4                 | GPIO_IO13        |                 |           | 0        | V_GPIO | P20         |                                              |

|                    |                  | UART3_TXD       | UART      | -        |        |             |                                              |

| T4                 | GPIO_IO15        | UART3_RXD       | UART      | 1        | V_GPIO | P21         |                                              |

| T2                 | GPIO_IO16        | SAI3_TXC        | SAI       | 0        | V_GPIO | R21         |                                              |

| T1                 | GPIO_IO17        | SAI3_MCLK       | SAI       | 0        | V_GPIO | R20         |                                              |

| R2                 | GPIO_IO18        | SAI3_RXC        | SAI       | -        | V_GPIO | R18         |                                              |

| P3                 | GPIO_IO19        | SAI3_RXFS       | SAI       | ı        | V_GPIO | R17         |                                              |

| N2                 | GPIO_IO20        | SAI3_RXD0       | SAI       | ı        | V_GPIO | T20         |                                              |

| R3                 | GPIO_IO21        | SAI3_TXD0       | SAI       | 0        | V_GPIO | T21         |                                              |

| P5                 | GPIO_IO22        | I2C5_SDA        | I2C       | I/O      | V_GPIO | U18         | Need external pull-ups if used as I2C5       |

| P4                 | GPIO_IO23        | I2C5_SCL        | I2C       | 0        | V_GPIO | U20         | Need external pull-ups if used as I2C5       |

| N5                 | GPIO_IO24        | GPIO2_IO24      | GPIO      | I/O      | V_GPIO | U21         |                                              |

| M5                 | GPIO_IO25        | CAN2_TX         | CAN       | 0        | V_GPIO | V21         |                                              |

| N4                 | GPIO_IO26        | SAI3_TXFS       | SAI       | 0        | V_GPIO | V20         |                                              |

| L5                 | GPIO_IO27        | CAN2_RX         | CAN       | _        | V_GPIO | W21         |                                              |

| L4                 | GPIO_IO28        | I2C3_SDA        | I2C       | I/O      | V_GPIO | W20         | Need external<br>pull-ups if used as<br>I2C3 |

| K4                 | GPIO_IO29        | I2C3_SCL        | I2C       | 0        |        |             | Need external<br>pull-ups if used as<br>I2C3 |

| C10                | I2C1_SCL         | I2C1_SCL        | I2C       | 0        | 3,3 V  | C20         |                                              |

| C9                 | I2C1_SDA         | I2C1_SDA        | I2C       | I/O      | 3,3 V  | C21         |                                              |

| T15                | I2C2_SCL         | GPIO1_IO02      | GPIO      | I/O      | 3,3 V  | D20         |                                              |

| B16                | ISO_14443_LA     | ISO_14443_LA    | ISO_14443 | I/O      | 3,3 V  | -           |                                              |

| C17                | ISO_14443_LB     | ISO_14443_LB    | ISO_14443 | I/O      | 3,3 V  | -           |                                              |

| A15                | ISO_7816_CLK     | ISO_7816_CLK    | ISO_7816  | ı        | 3,3 V  | -           |                                              |

| A17                | ISO_7816_IO1     | ISO_7816_IO1    | ISO_7816  | I/O      | 3,3 V  | -           |                                              |

| B15                | ISO_7816_IO2     | ISO_7816_IO2    | ISO_7816  | I/O      | 3,3 V  | -           |                                              |

| D16                | ISO_7816_RST_N   | ISO_7816_RST    | ISO_7816  | I        | 3,3 V  | -           |                                              |

| D19                | LVDS_CLK_N       | LVDS_CLK_N      | LVDS      | 0        | 1,8 V  | А3          |                                              |

| C19                | LVDS_CLK_P       | LVDS_CLK_P      | LVDS      | 0        | 1,8 V  | В3          |                                              |

| G19                | LVDS_D0_N        | LVDS_D0_N       | LVDS      | 0        | 1,8 V  | A5          |                                              |

| F19                | LVDS_D0_P        | LVDS_D0_P       | LVDS      | 0        | 1,8 V  | B5          |                                              |

| F17                | LVDS_D1_N        | LVDS_D1_N       | LVDS      | 0        | 1,8 V  | A4          |                                              |

| E17                | LVDS_D1_P        | LVDS_D1_P       | LVDS      | 0        | 1,8 V  | В4          |                                              |

| E18                | LVDS_D2_N        | LVDS_D2_N       | LVDS      | 0        | 1,8 V  | A2          |                                              |

| D18                | LVDS_D2_P        | LVDS_D2_P       | LVDS      | 0        | 1,8 V  | B2          |                                              |

| B18                | LVDS_D3_N        | LVDS_D3_N       | LVDS      | 0        | 1,8 V  | B1          |                                              |

| A18                | LVDS_D3_P        | LVDS_D3_N       | LVDS      | 0        | 1,8 V  | C1          |                                              |

|                    |                  |                 |           | <u> </u> | .,~ •  |             | ı                                            |

Table 3: TQMa93xxLA, signals (continued)

| Table 3.           | TQIVIA93XXLA, SIGITA | is (continuca)  |        |      |             |             |                                      |

|--------------------|----------------------|-----------------|--------|------|-------------|-------------|--------------------------------------|

| TQMa93xxLAA<br>pad | Ball name            | TQ multiplexing | Group  | Dir. | Level       | CPU<br>ball | Comment                              |

| N18                | MIPI_CSI1_CLK_N      | CSI_CLK_N       | CSI    |      | 1,8 V       | D10         |                                      |

| P18                | MIPI_CSI1_CLK_P      | CSI_CLK_P       | CSI    | I    | 1,8 V       | E10         |                                      |

| M19                | MIPI_CSI1_D0_N       | CSI_D0_N        | CSI    | ı    | 1,8 V       | A11         |                                      |

| N19                | MIPI_CSI1_D0_P       | CSI_D0_P        | CSI    | ı    | 1,8 V       | B11         |                                      |

| P19                | MIPI_CSI1_D1_N       | CSI_D1_N        | CSI    | ı    | 1,8 V       | A10         |                                      |

| R19                | MIPI_CSI1_D1_P       | CSI_D1_P        | CSI    | I    | 1,8 V       | B10         |                                      |

| J19                | MIPI_DSI1_CLK_N      | DSI_CLK_N       | DSI    | 0    | 1,8 V       | D6          |                                      |

| K19                | MIPI_DSI1_CLK_P      | DSI_CLK_P       | DSI    | 0    | 1,8 V       | E6          |                                      |

| G18                | MIPI_DSI1_D0_N       | DSI_D0_N        | DSI    | 0    | 1,8 V       | A6          |                                      |

| H18                | MIPI_DSI1_D0_P       | DSI_D0_P        | DSI    | 0    | 1,8 V       | В6          |                                      |

| H17                | MIPI_DSI1_D1_N       | DSI_D1_N        | DSI    | 0    | 1,8 V       | A7          |                                      |

| J17                | MIPI_DSI1_D1_P       | DSI_D1_P        | DSI    | 0    | 1,8 V       | В7          |                                      |

| K18                | MIPI_DSI1_D2_N       | DSI_D2_N        | DSI    | 0    | 1,8 V       | A8          |                                      |

| L18                | MIPI_DSI1_D2_P       | DSI_D2_P        | DSI    | 0    | 1,8 V       | В8          |                                      |

| L17                | MIPI_DSI1_D3_N       | DSI_D3_N        | DSI    | 0    | 1,8 V       | A9          |                                      |

| M17                | MIPI_DSI1_D3_P       | DSI_D3_P        | DSI    | 0    | 1,8 V       | B9          |                                      |

| G7                 | ONOFF                | ONOFF           | Config | ı    | 1,8 V       | A19         |                                      |

| G16                | PDM_BIT_STREAM0      | CAN1_RX         | CAN    | i    | 3,3 V       | J17         |                                      |

| E16                | PDM_BIT_STREAM1      | M33_NMI         | GPIO   | I    | 3,3 V       | G18         | Non maskable interrupt of M33 Copro. |

| H16                | PDM_CLK              | CAN1_TX         | CAN    | 0    | 3,3 V       | G17         |                                      |

| E6                 | PMIC_RST_B           | PMIC_RST#       | Config | I    | 1,8 V       | -           |                                      |

| J5                 | RESET_OUT#           | RESET_OUT#      | Config | 0    | OD          | -           | Open-Drain (up to 5,5 V)             |

| E14                | RTC_EVENT#           | RTC_EVENT#      | Config | 0    | OD          | -           | Open-Drain (0,7<br>V to 5,5 V)       |

| V10                | SAI1_RXD0            | GPIO1_IO14      | GPIO   | I/O  | 3,3 V       | H20         |                                      |

| V11                | SAI1_TXC             | GPIO1_IO12      | GPIO   | I/O  | 3,3 V       | G20         |                                      |

| W10                | SAI1_TXD0            | UART2_RTS#      | UART   | 0    | 3,3 V       | H21         | Used as<br>BOOT_MODE3<br>at startup  |

| U10                | SAI1_TXFS            | GPIO1_IO11      | GPIO   | I/O  | 3,3 V       | G21         | Used as<br>BOOT_MODE2<br>at startup  |

| G5                 | SCLH                 | PMIC_SCLH       | LVLTRL | I/O  | 3,3 V       | -           |                                      |

| H5                 | SCLL                 | PMIC_SCLL       | LVLTRL | I/O  | 1,8 V       | -           |                                      |

| U2                 | SD2_CD_B             | SD2_CD#         | SD     | ı    | 1,8 / 3,3 V | Y17         |                                      |

| W2                 | SD2_CLK              | SD2_CLK         | SD     | 0    | 1,8 / 3,3 V | AA19        |                                      |

| W3                 | SD2_CMD              | SD2_CMD         | SD     | I/O  | 1,8 / 3,3 V | Y19         |                                      |

| V4                 | SD2_DATA0            | SD2_DATA0       | SD     | I/O  | 1,8 / 3,3 V | Y18         |                                      |

| V3                 | SD2_DATA1            | SD2_DATA1       | SD     | I/O  | 1,8 / 3,3 V | AA18        |                                      |

| U3                 | SD2_DATA2            | SD2_DATA2       | SD     | I/O  | 1,8 / 3,3 V | Y20         |                                      |

| V1                 | SD2_DATA3            | SD2_DATA3       | SD     | I/O  | 1,8 / 3,3 V | AA20        |                                      |

| U1                 | SD2_RST_B            | SD2_RST#        | SD     | 0    | 1,8 / 3,3 V | AA17        |                                      |

| V14                | SD3_CLK              | QSPI_SCLK       | QSPI   | 0    | 1,8 V       | V16         |                                      |

| U13                | SD3_CMD              | QSPI_SS0#       | QSPI   | 0    | 1,8 V       | U16         |                                      |

| V13                | SD3_DATA0            | QSPI_DATA0      | QSPI   | I/O  | 1,8 V       | T16         |                                      |

| U12                | SD3_DATA1            | QSPI_DATA1      | QSPI   | I/O  | 1,8 V       | V14         |                                      |

| W13                | SD3_DATA2            | QSPI_DATA2      | QSPI   | I/O  | 1,8 V       | U14         |                                      |

| W12                | SD3_DATA3            | QSPI_DATA3      | QSPI   | I/O  | 1,8 V       | T14         |                                      |

| G4                 | SDAH                 | PMIC_SDAH       | LVLTRL | I/O  | 3,3 V       | -           |                                      |

| H4                 | SDAL                 | PMIC_SDAL       | LVLTRL | I/O  | 1,8 V       | -           |                                      |

|                    |                      |                 |        |      |             |             |                                      |

Table 3: TQMa93xxLA, signals (continued)

| Table 5:                                                                                                                          | rQivia95xxLA, signais (cor                                                                                                                                                                                                                                                                               | itiliaca)       |        |      |             |             |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|------|-------------|-------------|--------------------------------------|

| TQMa93xxLAA<br>pad                                                                                                                | Ball name                                                                                                                                                                                                                                                                                                | TQ multiplexing | Group  | Dir. | Level       | CPU<br>ball | Comment                              |

| L16                                                                                                                               | TAMPER0                                                                                                                                                                                                                                                                                                  | TAMPER0         | Tamper | I/O  | 1,8 V       | B16         |                                      |

| K16                                                                                                                               | TAMPER1                                                                                                                                                                                                                                                                                                  | TAMPER1         | Tamper | I/O  | 1,8 V       | F14         |                                      |

| F15                                                                                                                               | TEMP_EVENT#                                                                                                                                                                                                                                                                                              | TEMP_EVENT#     | Config | 0    | OD          | _           | Open-Drain                           |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                          |                 | , ,    |      |             |             | (0,9 V to 3,6 V)                     |

| D10                                                                                                                               | UART1_RXD                                                                                                                                                                                                                                                                                                | UART1_RXD       | UART   | ı    | 3,3 V       | E21         |                                      |

| D11                                                                                                                               | UART1_TXD                                                                                                                                                                                                                                                                                                | UART1_TXD       | UART   | 0    | 3,3 V       | E21         | Used as BOOT_MODE0 at startup.       |

| E12                                                                                                                               | UART2_RXD                                                                                                                                                                                                                                                                                                | UART2_RXD       | UART   | ı    | 3,3 V       | F20         | '                                    |

| E11                                                                                                                               | UART2_TXD                                                                                                                                                                                                                                                                                                | UART2_TXD       | UART   | 0    | 3,3 V       | F21         | Used as<br>BOOT_MODE1<br>at startup. |

| V19                                                                                                                               | USB1_D_N                                                                                                                                                                                                                                                                                                 | USB1 DN         | USB    | I/O  | 3,3 V       | A14         | '                                    |

| U19                                                                                                                               | USB1_D_P                                                                                                                                                                                                                                                                                                 | USB1_DP         | USB    | 1/0  | 3,3 V       | B14         |                                      |

| N16                                                                                                                               | USB1_ID                                                                                                                                                                                                                                                                                                  | USB1_ID         | USB    | 1    | 1,8 V       | C11         |                                      |

| P17                                                                                                                               | USB1_VBUS                                                                                                                                                                                                                                                                                                | USB1_VBUS       | USB    | P    | 5 V         | F12         |                                      |

| W18                                                                                                                               | USB2_D_N                                                                                                                                                                                                                                                                                                 | USB2_DN         | USB    | I/O  | 3,3 V       | A15         |                                      |

| V18                                                                                                                               | USB2_D_P                                                                                                                                                                                                                                                                                                 | USB2_DP         | USB    | 1/0  | 3,3 V       | B15         |                                      |

| P16                                                                                                                               | USB2_ID                                                                                                                                                                                                                                                                                                  | USB2_ID         | USB    | 1/ 0 | 1,8 V       | E12         |                                      |

| T16                                                                                                                               | USB2_VBUS                                                                                                                                                                                                                                                                                                | USB2_VBUS       | USB    | P    | 5 V         | E14         |                                      |

| K6                                                                                                                                | WDOG_ANY                                                                                                                                                                                                                                                                                                 | WDOG_ANY        | GPIO   | 0    | 3,3 V       | J18         |                                      |

| H6                                                                                                                                | WDOG_ANT                                                                                                                                                                                                                                                                                                 | PMIC_WDOG_IN#   | Config | ı    | 3,3 V       | 710         |                                      |

| M6, N6, E7,                                                                                                                       | WDOG_B                                                                                                                                                                                                                                                                                                   | PMIC_WDOG_IN#   | Coning | ı    | 3,3 V       |             |                                      |

| D8, C12, F12,<br>T12, C13, D13,<br>F13, C14                                                                                       | -                                                                                                                                                                                                                                                                                                        | RFU             | -      | -    | -           | -           | Reserved for future use              |

| T17, U17, R18,<br>T18                                                                                                             | -                                                                                                                                                                                                                                                                                                        | DNC             | -      | -    | 1           | ı           | Do not connect                       |

| N1                                                                                                                                | V_1V8                                                                                                                                                                                                                                                                                                    | V_1V8           | Power  | Р    | 1,8 V       | 1           | Power-Output (max. 500 mA)           |

| P1                                                                                                                                | V_3V3                                                                                                                                                                                                                                                                                                    | V_3V3           | Power  | Р    | 3,3 V       | ı           | Power-Output (max. 500 mA)           |

| F6                                                                                                                                | V_3V3_SD                                                                                                                                                                                                                                                                                                 | V_3V3_SD        | Power  | Р    | 3,3 V       | ı           | Power-Output<br>(max. 400 mA)        |

| A2                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| A3                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| В3                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| C3                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| A4                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| B4                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| C4                                                                                                                                | V_5V_IN                                                                                                                                                                                                                                                                                                  | V_5V_IN         | Power  | Р    | 5 V         | -           | Power-Input                          |

| W9                                                                                                                                | V_GPIO                                                                                                                                                                                                                                                                                                   | V_GPIO          | Power  | Р    | 1,8 / 3,3 V | N15,<br>N16 | Power-Input                          |

| D15                                                                                                                               | V_LICELL                                                                                                                                                                                                                                                                                                 | V_LICELL        | Power  | Р    | 3 V         | -           | Power-Input                          |

| T11                                                                                                                               | V_SD2                                                                                                                                                                                                                                                                                                    | V_SD2           | Power  | Р    | 1,8 / 3,3 V | -           | Power-Output<br>(max. 75 mA)         |

| E3, F3, G3, K3,I<br>W4, A5, B5, C5,<br>G6, J6, L6, P6,<br>W7, A8, C8, E8,<br>C11, F11, U11,<br>D14, F14, U14,<br>C16, F16, J16, N | B2, C2, E2, H2, L2, P2,V2, D3, N3, T3, D4, E4, F4, J4, M4, U4, D5, E5, F5, K5, R5, V5, C6, D6, T6, B7, D7, F7, H7, R7, U7, V7, G8, D9, V9, B10, E10, T10, A11, W11, D12, V12, E13, T13, A14, W14,C15, E15, G15, V15, A16, M16, R16, U16, B17, D17, G17, V17, C18, F18, J18, M18, U18, E19, H19, L19, T19 | Ground          | Power  | Р    | 0 V         | -           |                                      |

Table 3: TQMa93xxLA, signals (continued)

| TQMa93xxLAA<br>pad                                                                                                                                                                                                                                                                                                                                                                    | Ball name | TQ multiplexing | Group | Dir. | Level | CPU<br>ball | Comment          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|-------|------|-------|-------------|------------------|

| A1, W1, J7, K7, L7, M7, N7, P7, H8, J8, K8, L8, M8, N8, P8, R8, G9, H9, J9, K9, L9, M9, N9, P9, R9, G10, H10, J10, K10, L10, M10, N10, P10, R10, G11, H11, J11, K11, L11, M11, N11, P11, R11, G12, H12, J12, K12, L12, M12, N12, P12, R12, G13, H13, J13, K13, L13, M13, N13, P13, R13, G14, H14, J14, K14, L14, M14, N14, P14, R14, H15, J15, K15, L15, M15, N15, P15, R15, A19, W19 | -         | Not available   | -     | -    | -     | -           | Not<br>available |

# 3.2 System components

#### 3.2.1 i.MX 93

#### 3.2.1.1 i.MX 93 derivatives

Depending on the TQMa93xxLA version, one of the following i.MX 93 derivatives is assembled.

Table 4: i.MX 93 derivatives

| TQMa93xxLA version | i.MX 93 derivative | i.MX 93 clocks                      | Temperature range |

|--------------------|--------------------|-------------------------------------|-------------------|