# MBa8x User's Manual

MBa8x UM Rev. 0101 07.07.2022

# TABLE OF CONTENTS

| 1.       | ABOUT THIS MANUAL                                 |    |

|----------|---------------------------------------------------|----|

| 1.1      | Copyright and license expenses                    |    |

| 1.2      | Registered trademarks                             | 6  |

| 1.3      | Disclaimer                                        | 6  |

| 1.4      | Imprint                                           | 6  |

| 1.5      | Tips on safety                                    | 7  |

| 1.6      | Symbols and typographic conventions               | 7  |

| 1.7      | Handling and ESD tips                             | 7  |

| 1.8      | Naming of signals                                 |    |

| 1.9      | Further applicable documents / presumed knowledge |    |

| 2.       | BRIEF DESCRIPTION                                 |    |

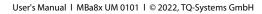

| 2.1      | MBa8x block diagram                               |    |

| 2.2      | MBa8x interfaces                                  |    |

| 3.       | ELECTRONICS                                       |    |

| 3.1      | MBa8x functional groups                           |    |

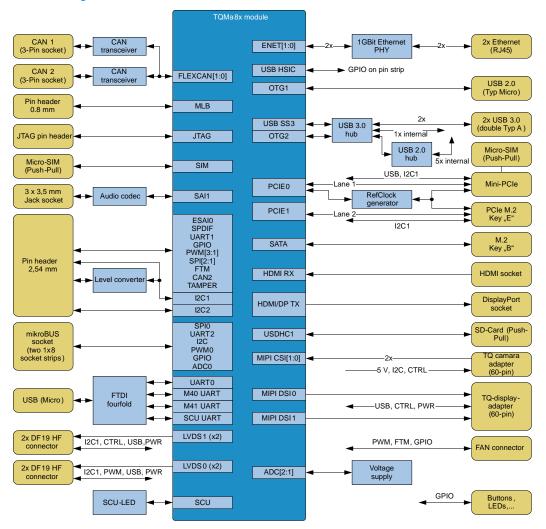

| 3.2      | TQMa8x                                            |    |

| 3.3      | TQMa8x mating connectors                          |    |

| 3.4      | TQMa8x pinout                                     |    |

| 3.5      | Boot-Mode configuration                           |    |

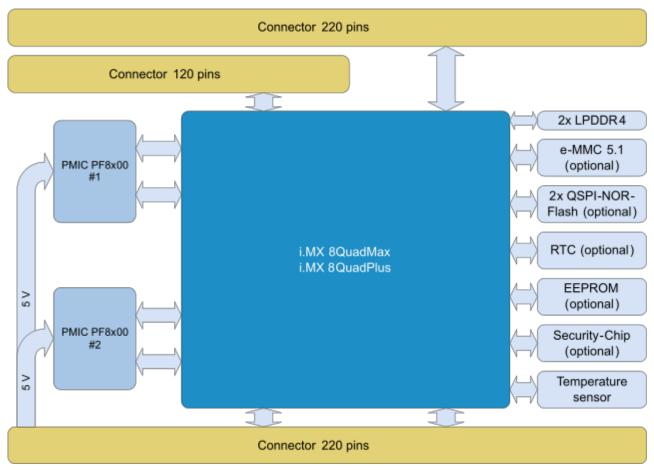

| 3.6      | Reset and Power Modes                             |    |

| 3.7      | General purpose push buttons                      |    |

|          | Battery                                           |    |

| 3.8      | ·                                                 |    |

| 3.9      | LEDs                                              |    |

| 3.10     | I <sup>2</sup> C devices                          |    |

| 3.11     | GPIO port expander                                |    |

| 3.12     | Temperature sensor                                |    |

| 3.13     | Further devices                                   |    |

| 3.14     | Interfaces                                        |    |

| 3.14.1   | Audio                                             |    |

| 3.14.2   | SPDIF                                             |    |

| 3.14.3   | CAN-FD                                            |    |

| 3.14.4   | MLB                                               |    |

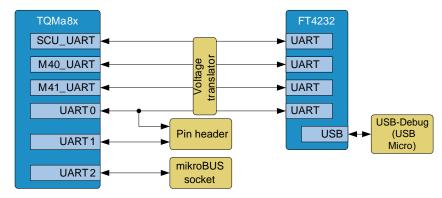

| 3.14.5   | USB debug                                         |    |

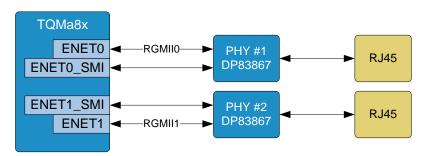

| 3.14.6   | Ethernet                                          |    |

| 3.14.7   | GPIO                                              |    |

| 3.14.8   | Display interfaces                                | 28 |

| 3.14.8.1 | DisplayPort                                       |    |

| 3.14.8.2 | HDMI In                                           | 29 |

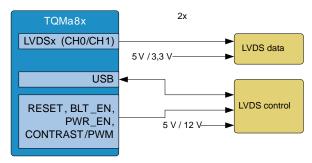

| 3.14.8.3 | LVDS                                              | 29 |

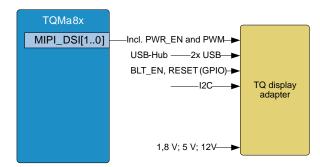

| 3.14.8.4 | MIPI DSI                                          | 29 |

| 3.14.9   | MIPI CSI                                          | 30 |

| 3.14.10  | Mini PCle                                         | 32 |

| 3.14.11  | PCIe M.2                                          | 32 |

| 3.14.12  | PCIe-Clock                                        | 32 |

| 3.14.13  | SATA M.2                                          | 33 |

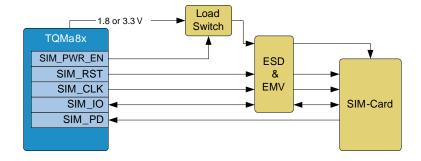

| 3.14.14  | SIM                                               | 33 |

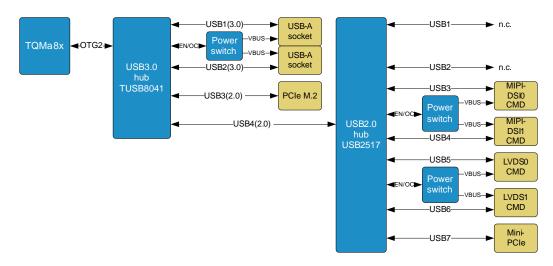

| 3.14.15  | USB hosts/hubs                                    |    |

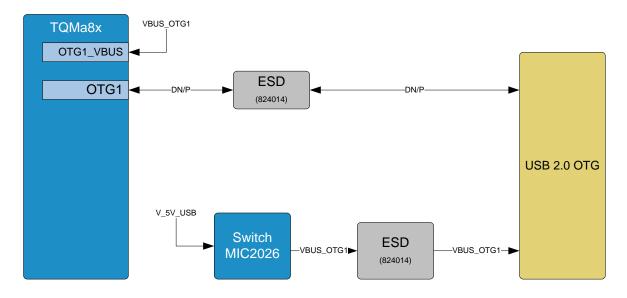

| 3.14.16  | USB OTG                                           |    |

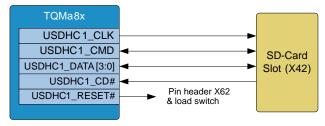

| 3.14.17  | SD card                                           |    |

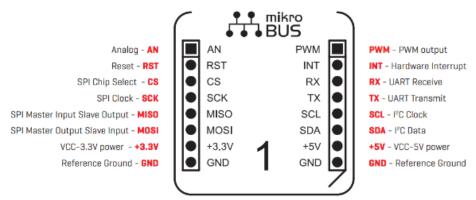

| 3.14.18  | mikroBUS                                          |    |

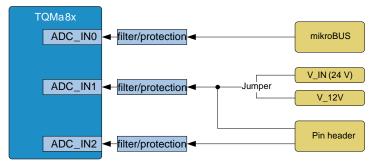

| 3.14.19  | ADC                                               |    |

| 3.14.19  |                                                   |    |

|          | MBa8x headers                                     |    |

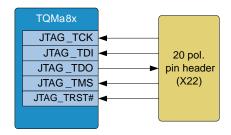

| 3.14.21  | JTAG                                              |    |

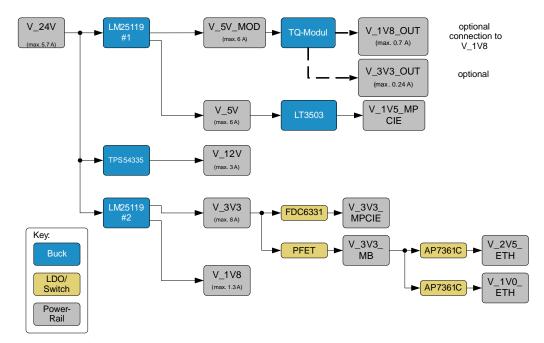

| 3.15     | Power supply                                      |    |

| 3.16     | Cooling concept                                   |    |

| 3.17     | Fan                                               |    |

| 4.<br>-  | SOFTWARE                                          |    |

| 5.       | MECHANICS                                         |    |

| 5.1      | MBa8x dimensions                                  |    |

| 5.2      | Notes of treatment                                |    |

| 5.3      | Embedding in the target system                    | 43 |

| 5.4 | Thermal management                             | 43 |

|-----|------------------------------------------------|----|

| 5.5 | Thermal management                             | 44 |

| 6.  | SAFETY REQUIREMENTS AND PROTECTIVE REGULATIONS | 46 |

| 6.1 | EMC                                            | 46 |

| 6.2 | ESD                                            | 46 |

| 6.3 | Operational safety and personal security       | 46 |

| 7.  | CLIMATIC AND OPERATIONAL CONDITIONS            | 46 |

| 7.1 | Protection against external effects            | 46 |

| 7.2 | Reliability and service life                   |    |

| 8.  | ENVIRONMENT PROTECTION                         | 47 |

| 8.1 | RoHS                                           |    |

| 8.2 | WEEE <sup>®</sup>                              | 47 |

| 8.3 | REACH®                                         |    |

| 8.4 | EuP                                            | 47 |

| 8.5 | Packaging                                      | 47 |

| 8.6 | Batteries                                      |    |

| 8.7 | General notes                                  |    |

| 8.8 | Lithium batteries                              |    |

| 8.9 | Other entries                                  | 47 |

| 9.  | APPENDIX                                       |    |

| 9.1 | Acronyms and definitions                       | 48 |

| 9.2 | References                                     | 50 |

# TABLE DIRECTORY

| Table 1:  | Terms and Conventions                                         | 7  |

|-----------|---------------------------------------------------------------|----|

| Table 2:  | MBa8x interfaces and auxiliary functions                      | 10 |

| Table 3:  | Diagnostic and user interfaces                                | 11 |

| Table 4:  | Carrier board mating connectors                               | 13 |

| Table 5:  | Pinout TQMa8x connector X1                                    | 14 |

| Table 6:  | Pinout TQMa8x connector X2                                    | 16 |

| Table 7:  | Pinout TQMa8x connector X3                                    | 18 |

| Table 8:  | Boot-Mode configuration                                       |    |

| Table 9:  | Reset and Power Mode signals                                  | 20 |

| Table 10: | I <sup>2</sup> C devices, address mapping on TQMa8x and MBa8x | 23 |

| Table 11: | Functions port expander                                       | 24 |

| Table 12: | Placement option Audio                                        | 24 |

| Table 13: | CAN termination                                               | 25 |

| Table 14: | Pinout X21                                                    | 25 |

| Table 15: | Ethernet Reset and Interrupt signals                          | 26 |

| Table 16: | Characteristics Ethernet 0 (X39)                              | 27 |

| Table 17: | Characteristics Ethernet 1 (X40)                              | 27 |

| Table 18: | GPIO signals                                                  | 28 |

| Table 19: | TQ MIPI-DSI adapter                                           | 30 |

| Table 20: | TQ MIPI-CSI adapter                                           | 31 |

| Table 21: | Power-Distribution TUSB8041                                   | 34 |

| Table 22: | Properties USB host 1 and 2                                   | 34 |

| Table 23: | Properties of USB-OTG                                         |    |

| Table 24: | mikroBus signals                                              | 36 |

| Table 25: | Values ADC circuit                                            | 37 |

| Table 26: | Current consumption headers                                   | 37 |

| Table 27: | Pinout Header X61                                             | 37 |

| Table 28: | Pinout Header X62                                             | 38 |

| Table 29: | Pinout Header X63                                             | 38 |

| Table 30: | Pinout Header X64                                             | 39 |

| Table 31: | Labels on MBa8x                                               | 45 |

| Table 32: | Climatic and operational conditions MBa8x                     | 46 |

| Table 33: | Acronyms                                                      | 48 |

| Table 34: | Further applicable documents                                  | 50 |

|           |                                                               |    |

# FIGURE DIRECTORY

| Figure 2: Block diagram TQMa8x.   1 Figure 3: Block diagram Reset.   7 Figure 4: Placement push buttons on MBa8X   7 Figure 9: Block diagram Bettery.   7 Figure 9: Block diagram PC bus.   7 Figure 10: Block diagram PC bus.   7 Figure 11: Block diagram LVDS   7 Figure 12: Block diagram LVDS   7 Figure 13: Block diagram LVDS   7 Figure 14: Block diagram MIPI-DSI   7 Figure 15: Block diagram MIPI-DSI   7 Figure 17: Block diagram MIPI-DSI   7 Figure 18: Block diagram MIPI-CSI / TQ Camera Interface   7 Figure 19: Clock supply PCle   7 Figure 19: Clock supply PCle   7 Figure 19: Block diagram MIPI-CSI / TQ Camera Interface   7 Figure 19: Clock supply PCle   7 Figure 19: Clock supply PCle   7 Figure 21: Block diagram SIM card   7 Figure 22: Block diagram DS bub structure of the MBa8x   7 Figure 23: Block diagram SD card   7 Figure 25: Block diagram ADC   7 Figure 26: Block diagram SDC and   7 Figure 27: Block diagram SDC   7 Figure 28: Position of heat sink mounting holes   7 Figure 29: MBa8x dimensions   7 Figure 29: MBa8x component placement top.   7 Figure 31: MBa8x, component placement bottom   7 Figure 32: MBa8x component placement bottom   7 Figure 32: MBa8x component placement bottom   7 Figure 32: MBa8x component placement bottom   7 Figure 30: MBa8x, component placement bottom   7 Figure 30: MBa8x component placement bottom   7 Figure 30: MBa8x, component placement bottom   7 Figure 30: MBa8x, component placement bottom   7 Figure 30: MBa8x component placement bottom | Figure 1:  | Block diagram MBa8x                          | 99 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------|----|

| Figure 4: Placement push buttons on MBa8X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 2:  | Block diagram TQMa8x                         | 12 |

| Figure 5: Block diagram GP push buttons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 3:  | Block diagram Reset                          | 19 |

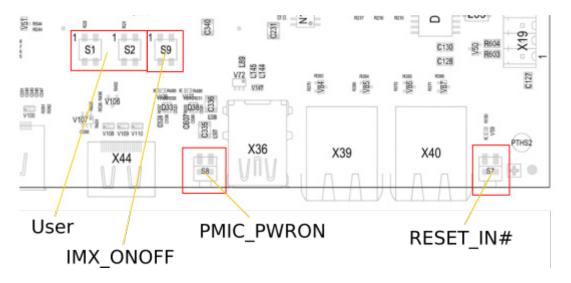

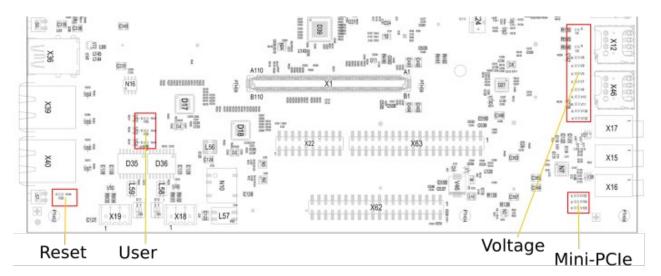

| Figure 6: Block diagram battery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 4:  | Placement push buttons on MBa8X              | 20 |

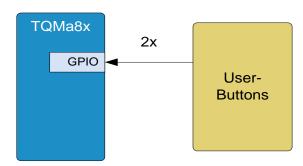

| Figure 7: Block diagram LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 5:  | Block diagram GP push buttons                | 20 |

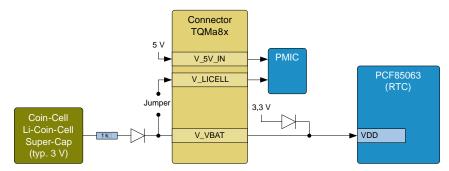

| Figure 8: Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 6:  | Block diagram battery                        | 21 |

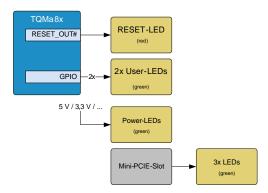

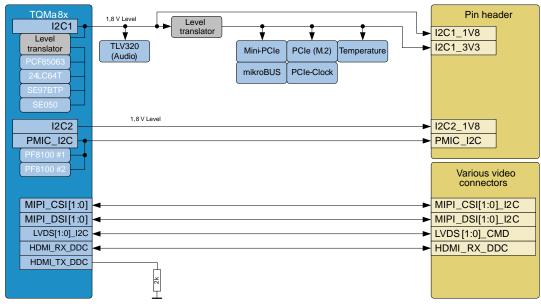

| Figure 9: Block diagram I²C bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 7:  | Block diagram LEDs                           | 21 |

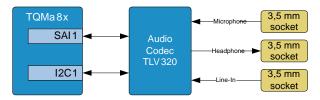

| Figure 10: Block diagram Audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 8:  | Placement                                    | 22 |

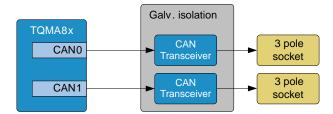

| Figure 11: Block diagram CAN-FD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 9:  | Block diagram I <sup>2</sup> C bus           | 22 |

| Figure 12: Block diagram USB debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 10: | Block diagram Audio                          | 24 |

| Figure 13: Block diagram Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 11: | Block diagram CAN-FD                         | 25 |

| Figure 14: Block diagram LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 12: | Block diagram USB debug                      | 26 |

| Figure 15: Block diagram MIPI-DSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 13: | Block diagram Ethernet                       | 26 |

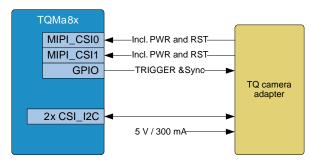

| Figure 16: Block diagram MIPI-CSI / TQ Camera Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 14: | Block diagram LVDS                           | 29 |

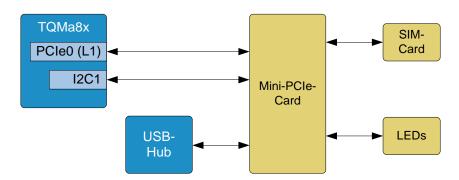

| Figure 17: Block diagram Mini-PCIe 3 Figure 18: Block diagram PCIe M.2 3 Figure 19: Clock supply PCIe 3 Figure 20: Block diagram SIM card 3 Figure 21: Block diagram USB hub structure of the MBa8x 3 Figure 22: Block diagram USB OTG 3 Figure 23: Block diagram SD card 3 Figure 24: Pinout microbus (source: MikroElektronika) 3 Figure 25: Block diagram ADC 3 Figure 26: Block diagram JTAG 3 Figure 27: Block diagram supply 4 Figure 28: Position of heat sink mounting holes 4 Figure 29: MBa8x dimensions 4 Figure 30: MBa8x, component placement top 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 15: | Block diagram MIPI-DSI                       | 30 |

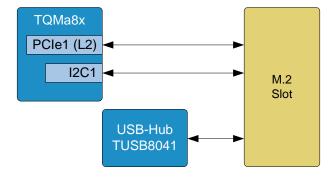

| Figure 18: Block diagram PCle M.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 16: | Block diagram MIPI-CSI / TQ Camera Interface | 31 |

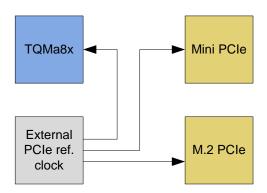

| Figure 19: Clock supply PCIe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 17: | Block diagram Mini-PCle                      | 32 |

| Figure 20: Block diagram SIM card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 18: | Block diagram PCIe M.2                       | 32 |

| Figure 21: Block diagram USB hub structure of the MBa8x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 19: | Clock supply PCIe                            | 33 |

| Figure 22: Block diagram USB OTG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 20: | Block diagram SIM card                       | 33 |

| Figure 23: Block diagram SD card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 21: | Block diagram USB hub structure of the MBa8x | 34 |

| Figure 24: Pinout microbus (source: MikroElektronika)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figure 22: | Block diagram USB OTG                        | 35 |

| Figure 25: Block diagram ADC 3 Figure 26: Block diagram JTAG 3 Figure 27: Block diagram supply 4 Figure 28: Position of heat sink mounting holes 4 Figure 29: MBa8x dimensions 4 Figure 30: MBa8x, component placement top 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 23: | Block diagram SD card                        | 35 |

| Figure 26: Block diagram JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 24: | Pinout microbus (source: MikroElektronika)   | 36 |

| Figure 27: Block diagram supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 25: | Block diagram ADC                            | 37 |

| Figure 28: Position of heat sink mounting holes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 26: | Block diagram JTAG                           | 39 |

| Figure 29: MBa8x dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 27: | Block diagram supply                         | 40 |

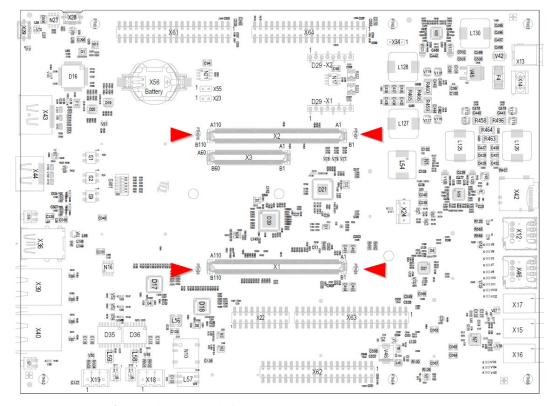

| Figure 30: MBa8x, component placement top                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 28: |                                              |    |

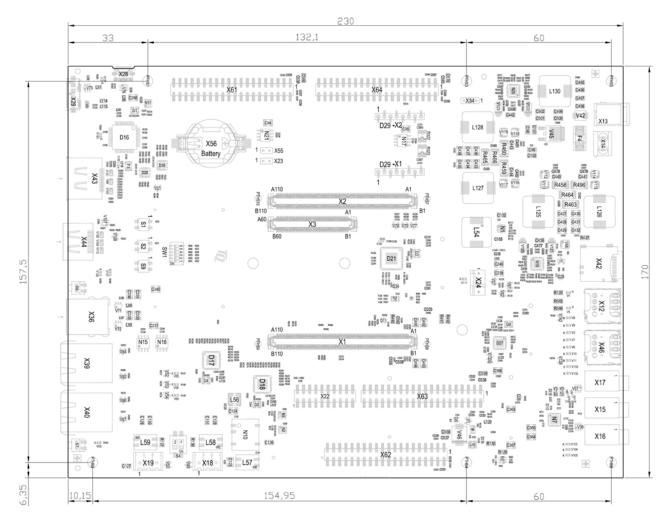

| , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 29: | MBa8x dimensions                             | 42 |

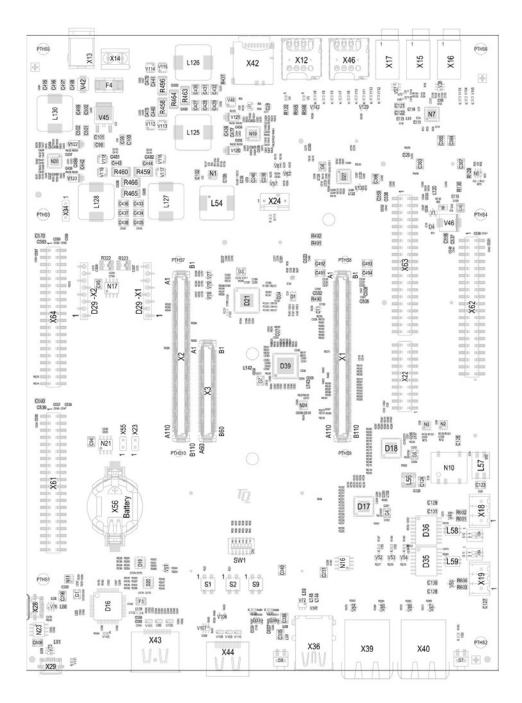

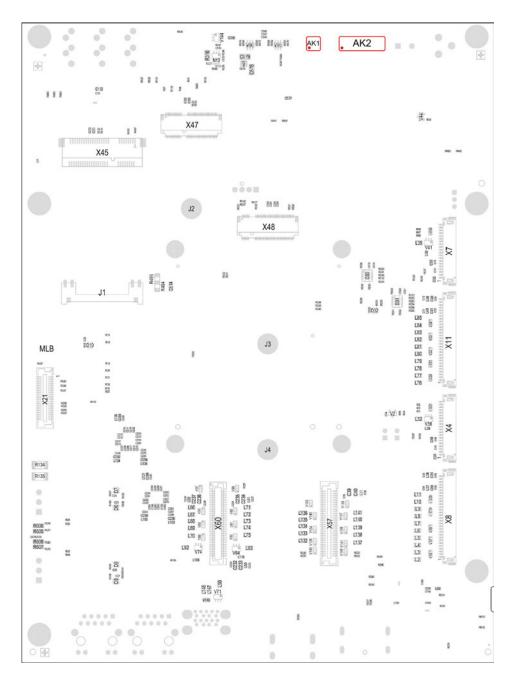

| Figure 31: MBa8x, component placement bottom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 30: | MBa8x, component placement top               | 44 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 31: | MBa8x, component placement bottom            | 45 |

# **REVISION HISTORY**

| Rev. | Date       | Name    | Pos. | Modification                         |

|------|------------|---------|------|--------------------------------------|

| 0100 | 29.11.2021 | Kreuzer |      | First edition                        |

| 0101 | 07.07.2022 | Kreuzer |      | Added footnotes to MIPI_CSI1_SCL/SDA |

## 1. ABOUT THIS MANUAL

# 1.1 Copyright and license expenses

Copyright protected © 2022 by TQ-Systems GmbH.

This User's Manual may not be copied, reproduced, translated, changed or distributed, completely or partially in electronic, machine readable, or in any other form without the written consent of TQ-Systems GmbH.

The drivers and utilities for the components used as well as the BIOS are subject to the copyrights of the respective manufacturers. The licence conditions of the respective manufacturer are to be adhered to.

Bootloader-licence expenses are paid by TQ-Systems GmbH and are included in the price.

Licence expenses for the operating system and applications are not taken into consideration and must be calculated / declared separately.

# 1.2 Registered trademarks

TQ-Systems GmbH aims to adhere to copyrights of all graphics and texts used in all publications, and strives to use original or license-free graphics and texts.

All brand names and trademarks mentioned in this User's Manual, including those protected by a third party, unless specified otherwise in writing, are subjected to the specifications of the current copyright laws and the proprietary laws of the present registered proprietor without any limitation. One should conclude that brand and trademarks are rightly protected by a third party.

## 1.3 Disclaimer

TQ-Systems GmbH does not guarantee that the information in this User's Manual is up-to-date, correct, complete or of good quality. Nor does TQ-Systems GmbH assume guarantee for further usage of the information. Liability claims against TQ-Systems GmbH, referring to material or non-material related damages caused, due to usage or non-usage of the information given in this User's Manual, or due to usage of erroneous or incomplete information, are exempted, as long as there is no proven intentional or negligent fault of TQ-Systems GmbH.

TQ-Systems GmbH explicitly reserves the rights to change or add to the contents of this User's Manual or parts of it without special notification.

# **Important Notice:**